|

upm

0.4.1

Sensor/Actuator repository for libmraa (v0.8.0)

|

|

upm

0.4.1

Sensor/Actuator repository for libmraa (v0.8.0)

|

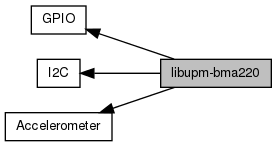

BMA220 Accelerometer library. More...

Data Structures | |

| class | BMA220 |

| API for the BMA220 3-axis Accelerometer. More... | |

Enumerations | |

| enum | REG_T { REG_CHIPID = 0x00, REG_REVISIONID = 0x02, REG_ACC_X = 0x04, REG_ACC_Y = 0x06, REG_ACC_Z = 0x08, REG_H_HYST_DUR = 0x0a, REG_THRESHOLD = 0x0c, REG_L_HYST_DUR = 0x0e, REG_TAP_CONFIG = 0x10, REG_SLOPE_CONFIG = 0x12, REG_TAP_CONFIG2 = 0x14, REG_INT_STATUS1 = 0x16, REG_INT_STATUS2 = 0x18, REG_ENABLE_CONFIG = 0x1a, REG_ENABLE_CONFIG2 = 0x1c, REG_ENABLE_CONFIG3 = 0x1e, REG_FILTER_CONFIG = 0x20, REG_SBIST_FSL_CONFIG = 0x22, REG_I2C_WATCHDOG = 0x2e, REG_SUSPEND = 0x30, REG_SOFTRESET = 0x32 } |

| enum | H_HYST_DUR_HIGH_BITS_T { H_HYST_DUR_HIGH_DUR0 = 0x01, H_HYST_DUR_HIGH_DUR1 = 0x02, H_HYST_DUR_HIGH_DUR2 = 0x04, H_HYST_DUR_HIGH_DUR3 = 0x08, H_HYST_DUR_HIGH_DUR4 = 0x10, H_HYST_DUR_HIGH_DUR5 = 0x20, _H_HYST_DUR_HIGH_DUR_MASK = 63, _H_HYST_DUR_HIGH_DUR_SHIFT = 0, H_HYST_DUR_HIGH_HY1 = 0x40, H_HYST_DUR_HIGH_HY2 = 0x80, _H_HYST_DUR_HIGH_HY_MASK = 3, _H_HYST_DUR_HIGH_HY_SHIFT = 6 } |

| enum | THRESHOLD_BITS_T { THRESHOLD_HIGH0 = 0x01, THRESHOLD_HIGH1 = 0x02, THRESHOLD_HIGH2 = 0x04, THRESHOLD_HIGH3 = 0x08, _THRESHOLD_HIGH_MASK = 15, _THRESHOLD_HIGH_SHIFT = 0, THRESHOLD_LOW0 = 0x10, THRESHOLD_LOW1 = 0x20, THRESHOLD_LOW2 = 0x40, THRESHOLD_LOW3 = 0x80, _THRESHOLD_LOW_MASK = 15, _THRESHOLD_LOW_SHIFT = 4 } |

| enum | L_HYST_DUR_LOW_BITS_T { L_HYST_DUR_LOW_DUR0 = 0x01, L_HYST_DUR_LOW_DUR1 = 0x02, L_HYST_DUR_LOW_DUR2 = 0x04, L_HYST_DUR_LOW_DUR3 = 0x08, L_HYST_DUR_LOW_DUR4 = 0x10, L_HYST_DUR_LOW_DUR5 = 0x20, _L_HYST_DUR_LOW_DUR_MASK = 63, _L_HYST_DUR_LOW_DUR_SHIFT = 0, L_HYST_DUR_LOW_HY1 = 0x40, L_HYST_DUR_LOW_HY2 = 0x80, _L_HYST_DUR_LOW_HY_MASK = 3, _L_HYST_DUR_LOW_HY_SHIFT = 6 } |

| enum | TAP_CONFIG_BITS_T { TAP_CONFIG_DUR0 = 0x01, TAP_CONFIG_DUR1 = 0x02, TAP_CONFIG_DUR2 = 0x04, _TAP_CONFIG_DUR_MASK = 7, _TAP_CONFIG_DUR_SHIFT = 0, TAP_CONFIG_THRESH0 = 0x08, TAP_CONFIG_THRESH1 = 0x10, TAP_CONFIG_THRESH2 = 0x20, TAP_CONFIG_THRESH3 = 0x40, _TAP_CONFIG_THRESH_MASK = 15, _TAP_CONFIG_THRESH_SHIFT = 3, TAP_CONFIG_FILTER = 0x80 } |

| enum | SLOPE_CONFIG_BITS_T { SLOPE_CONFIG_DUR0 = 0x01, SLOPE_CONFIG_DUR1 = 0x02, _SLOPE_CONFIG_DUR_MASK = 3, _SLOPE_CONFIG_DUR_SHIFT = 0, SLOPE_CONFIG_THRESH0 = 0x04, SLOPE_CONFIG_THRESH1 = 0x08, SLOPE_CONFIG_THRESH2 = 0x10, SLOPE_CONFIG_THRESH3 = 0x20, _SLOPE_CONFIG_THRESH_MASK = 15, _SLOPE_CONFIG_THRESH_SHIFT = 2, SLOPE_CONFIG_FILTER = 0x40, SLOPE_CONFIG_ORIENT_EX = 0x80 } |

| enum | TAP_CONFIG2_BITS_T { TAP_CONFIG2_SAMP0 = 0x01, TAP_CONFIG2_SAMP1 = 0x02, _TAP_CONFIG2_SAMP_MASK = 3, _TAP_CONFIG2_SAMP_SHIFT = 0, TAP_CONFIG2_ORIENT_BLOCK0 = 0x04, TAP_CONFIG2_ORIENT_BLOCK1 = 0x08, _TAP_CONFIG2_ORIENT_BLOCK_MASK = 3, _TAP_CONFIG2_ORIENT_BLOCK_SHIFT = 2, TAP_CONFIG2_TIP_EN = 0x10 } |

| enum | TAP_SAMP_T { TAP_SAMP_2 = 0, TAP_SAMP_4 = 1, TAP_SAMP_8 = 2, TAP_SAMP_16 = 3 } |

| enum | TAP_ORIENT_BLOCK_T { TAP_ORIENT_BLOCK_0 = 0, TAP_ORIENT_BLOCK_2 = 1, TAP_ORIENT_BLOCK_3 = 2, TAP_ORIENT_BLOCK_4 = 3 } |

| enum | INT_STATUS1_BITS_T { INT_STATUS1_SIGN = 0x01, INT_STATUS1_FIRST_Z = 0x02, INT_STATUS1_FIRST_Y = 0x04, INT_STATUS1_FIRST_X = 0x08, INT_STATUS1_ORIENT0 = 0x10, INT_STATUS1_ORIENT1 = 0x20, INT_STATUS1_ORIENT2 = 0x40, _INT_STATUS1_ORIENT_MASK = 7, _INT_STATUS1_ORIENT_SHIFT = 4, INT_STATUS1_ORIENT_INT = 0x80 } |

| enum | CONFIG_ORIENT_T { CONFIG_ORI_UP_PORT_UPRIGHT = 0, CONFIG_ORI_UP_PORT_UPSIDE_DOWN = 1, CONFIG_ORI_UP_LAND_LEFT = 2, CONFIG_ORI_UP_LAND_RIGHT = 3, CONFIG_ORI_DN_PORT_UPRIGHT = 4, CONFIG_ORI_DN_PORT_UPSIDE_DOWN = 5, CONFIG_ORI_DN_LAND_LEFT = 6, CONFIG_ORI_DN_LAND_RIGHT = 7 } |

| enum | INT_STATUS2_BITS_T { INT_STATUS2_SLOPE = 0x01, INT_STATUS2_DATA = 0x02, INT_STATUS2_HIGH = 0x04, INT_STATUS2_LOW = 0x08, INT_STATUS2_TAP = 0x10 } |

| enum | ENABLE_CONFIG_BITS_T { ENABLE_CONFIG_TT_Z = 0x01, ENABLE_CONFIG_TT_Y = 0x02, ENABLE_CONFIG_TT_X = 0x04, ENABLE_CONFIG_SLOPE_Z = 0x08, ENABLE_CONFIG_SLOPE_Y = 0x10, ENABLE_CONFIG_SLOPE_X = 0x20, ENABLE_CONFIG_ORIENT = 0x40, ENABLE_CONFIG_DATA = 0x80 } |

| enum | ENABLE_CONFIG2_BITS_T { ENABLE_CONFIG2_HIGH_Z = 0x01, ENABLE_CONFIG2_HIGH_Y = 0x02, ENABLE_CONFIG2_HIGH_X = 0x04, ENABLE_CONFIG2_LOW = 0x08, ENABLE_CONFIG2_LAT_INT0 = 0x10, ENABLE_CONFIG2_LAT_INT1 = 0x20, ENABLE_CONFIG2_LAT_INT2 = 0x40, _ENABLE_CONFIG2_LAT_INT_MASK = 7, _ENABLE_CONFIG2_LAT_INT_SHIFT = 4, ENABLE_CONFIG2_RESET_INT = 0x80 } |

| enum | CONFIG2_LAT_T { CONFIG2_LAT_UNLATCH = 0, CONFIG2_LAT_0_25 = 1, CONFIG2_LAT_0_5 = 2, CONFIG2_LAT_1 = 3, CONFIG2_LAT_2 = 4, CONFIG2_LAT_4 = 5, CONFIG2_LAT_8 = 6, CONFIG2_LAT_PERM = 7 } |

| enum | ENABLE_CONFIG3_BITS_T { ENABLE_CONFIG3_Z_CHAN = 0x01, ENABLE_CONFIG3_Y_CHAN = 0x02, ENABLE_CONFIG3_X_CHAN = 0x04, ENABLE_CONFIG3_SLEEP_DUR0 = 0x08, ENABLE_CONFIG3_SLEEP_DUR1 = 0x10, ENABLE_CONFIG3_SLEEP_DUR2 = 0x20, _ENABLE_CONFIG3_SLEEP_DUR_MASK = 7, _ENABLE_CONFIG3_SLEEP_DUR_SHIFT = 3, ENABLE_CONFIG3_SLEEP_EN = 0x40 } |

| enum | SLEEP_DUR_T { SLEEP_DUR_2MS = 0, SLEEP_DUR_10MS = 1, SLEEP_DUR_25MS = 2, SLEEP_DUR_50MS = 3, SLEEP_DUR_100MS = 4, SLEEP_DUR_500MS = 5, SLEEP_DUR_1S = 6, SLEEP_DUR_2S = 7 } |

| enum | FILTER_CONFIG_BITS_T { FILTER_CONFIG_FILTER0 = 0x01, FILTER_CONFIG_FILTER1 = 0x02, FILTER_CONFIG_FILTER2 = 0x04, FILTER_CONFIG_FILTER3 = 0x08, _FILTER_CONFIG_FILTER_MASK = 15, _FILTER_CONFIG_FILTER_SHIFT = 0, FILTER_CONFIG_SERIAL_HIGH_BW = 0x80 } |

| enum | FILTER_CONFIG_T { FILTER_CONFIG_1KHZ = 0, FILTER_CONFIG_500HZ = 1, FILTER_CONFIG_250HZ = 2, FILTER_CONFIG_125HZ = 3, FILTER_CONFIG_64HZ = 4, FILTER_CONFIG_32HZ = 5 } |

| enum | SBIST_FSL_CONFIG_BITS_T { REG_SBIST_FSL_RANGE0 = 0x01, REG_SBIST_FSL_RANGE1 = 0x02, _REG_SBIST_FSL_RANGE_MASK = 3, _REG_SBIST_FSL_RANGE_SHIFT = 0, REG_SBIST_FSL_SBIST0 = 0x04, REG_SBIST_FSL_SBIST1 = 0x08, _REG_SBIST_FSL_SBIST_MASK = 3, _REG_SBIST_FSL_SBIST_SHIFT = 2, REG_SBIST_FSL_SBIST_SIGN = 0x10 } |

| enum | FSL_RANGE_T { FSL_RANGE_2G = 0, FSL_RANGE_4G = 1, FSL_RANGE_8G = 2, FSL_RANGE_16G = 3 } |

| enum | SBIST_T { SBIST_OFF = 0, SBIST_X = 1, SBIST_Y = 2, SBIST_Z = 3 } |

| enum | I2C_WATCHDOG_BITS_T { I2C_WATCHDOG_SPI3 = 0x01, I2C_WATCHDOG_TO_SEL = 0x02, I2C_WATCHDOG_TO_EN = 0x04 } |

| enum REG_T |

BMA220 Accelerometer registers

| enum H_HYST_DUR_HIGH_BITS_T |

REG_H_HYST_DUR bits

| enum THRESHOLD_BITS_T |

REG_THRESHOLD bits

| enum L_HYST_DUR_LOW_BITS_T |

REG_L_HYST_DUR bits

| enum TAP_CONFIG_BITS_T |

REG_TAP_CONFIG bits

| enum SLOPE_CONFIG_BITS_T |

REG_SLOPE_CONFIG bits

| enum TAP_CONFIG2_BITS_T |

REG_TAP_CONFIG2 bits

| enum TAP_SAMP_T |

TAP_CONFIG2_SAMP values

| enum TAP_ORIENT_BLOCK_T |

TAP_CONFIG2_ORIENT_BLOCK values

| enum INT_STATUS1_BITS_T |

REG_INT_STATUS1 bits

| enum CONFIG_ORIENT_T |

INT_STATUS1_ORIENT values

These are values reported by the device if orientation detection is enabled.

| enum INT_STATUS2_BITS_T |

REG_INT_STATUS2 bits

| enum ENABLE_CONFIG_BITS_T |

REG_ENABLE_CONFIG bits

| enum ENABLE_CONFIG2_BITS_T |

REG_ENABLE_CONFIG2 bits

| enum CONFIG2_LAT_T |

ENABLE_CONFIG2_LAT values

These are values that define the interrupt latching behavior

| enum ENABLE_CONFIG3_BITS_T |

REG_ENABLE_CONFIG3 bits

| enum SLEEP_DUR_T |

ENABLE_CONFIG3_SLEEP_DUR values

These are values that define the length of time the device sleeps before sampling when in sleep mode.

| enum FILTER_CONFIG_BITS_T |

REG_FILTER_CONFIG bits

| enum FILTER_CONFIG_T |

FILTER_CONFIG_FILTER values

These are values that define the digital filtering frequency

| enum SBIST_FSL_CONFIG_BITS_T |

REG_SBIST_FSL_CONFIG bits

| enum FSL_RANGE_T |

REG_SBIST_FSL_RANGE values

These are values that define the Full Scale configuration

| enum SBIST_T |

REG_SBIST_FSL_SBIST values

These are values that enable self test mode

| enum I2C_WATCHDOG_BITS_T |

REG_I2C_WATCHDOG bits

|

1.8.9.1

1.8.9.1