|

upm

1.6.0

Sensor/Actuator repository for libmraa (v1.9.0)

|

|

upm

1.6.0

Sensor/Actuator repository for libmraa (v1.9.0)

|

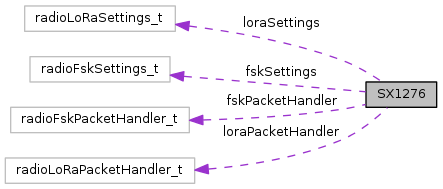

API for the SX1276 LoRa/FSK modem. More...

The SX1276 is a FSK/OOK/LoRa modem capable of both Low Frequency and High Frequency communication.

It requires a 3.3v power supply, do not use 5v.

Frequency Hopping Spread Spectrum (FHSS) is not currently supported.

While not all of the functionality of this device is supported initially, methods and register definitions are provided that should allow an end user to implement whatever features are required.

FSK send/receive example

LORA send/receive example

Public Types | |

| enum | RADIO_MODEM_T { MODEM_LORA = 0, MODEM_FSK } |

| enum | RADIO_EVENT_T { REVENT_DONE = 0, REVENT_EXEC, REVENT_ERROR, REVENT_TIMEOUT } |

| enum | SX1276_REGS_T { COM_RegFifo = 0x00, COM_RegOpMode = 0x01, FSK_RegBitrateMsb = 0x02, LOR_Reserved02 = 0x02, FSK_RegBitrateLsb = 0x03, LOR_Reserved03 = 0x03, FSK_RegFdevMsb = 0x04, LOR_Reserved04 = 0x04, FSK_RegFdevLsb = 0x05, LOR_Reserved05 = 0x05, COM_RegFrfMsb = 0x06, COM_RegFrfMid = 0x07, COM_RegFrfLsb = 0x08, COM_RegPaConfig = 0x09, COM_RegPaRamp = 0x0a, COM_RegOcp = 0x0b, COM_RegLna = 0x0c, FSK_RegRxConfig = 0x0d, LOR_RegFifoAddrPtr = 0x0d, FSK_RegRssiConfg = 0x0e, LOR_RegFifoTxBaseAddr = 0x0e, FSK_RegRssiCollision = 0x0f, LOR_RegFifoRxBaseAddr = 0x0f, FSK_RegRssiThresh = 0x10, LOR_RegFifoRxCurrentAddr = 0x10, FSK_RegRssiValue = 0x11, LOR_RegIrqFlagsMask = 0x11, FSK_RegRxBw = 0x12, LOR_RegIrqFlags = 0x12, FSK_RegAfcBw = 0x13, LOR_RegRxNbBytes = 0x13, FSK_RegOokPeak = 0x14, LOR_RegRxHeaderCntValueMsb = 0x14, FSK_RegOokFix = 0x15, LOR_RegRxHeaderCntValueLsb = 0x15, FSK_RegOokAvg = 0x16, LOR_RegRxPacketCntValueMsb = 0x16, FSK_Reserved17 = 0x17, LOR_RegRxPacketCntValueLsb = 0x17, FSK_Reserved18 = 0x18, LOR_RegModemStat = 0x18, FSK_Reserved19 = 0x19, LOR_RegPktSnrValue = 0x19, FSK_RegAfcFei = 0x1a, LOR_RegPktRssiValue = 0x1a, FSK_RegAfcMsb = 0x1b, LOR_RegRssiValue = 0x1b, FSK_RegAfcLsb = 0x1c, LOR_RegHopChannel = 0x1c, FSK_RegFeiMsb = 0x1d, LOR_RegModemConfig1 = 0x1d, FSK_RegFeiLsb = 0x1e, LOR_RegModemConfig2 = 0x1e, FSK_RegPreambleDetect = 0x1f, LOR_RegSymbTimeoutLsb = 0x1f, FSK_RegRxTimeout1 = 0x20, LOR_RegPreambleMsb = 0x20, FSK_RegRxTimeout2 = 0x21, LOR_RegPreambleLsb = 0x21, FSK_RegRxTimeout3 = 0x22, LOR_RegPayloadLength = 0x22, FSK_RegRxDelay = 0x23, LOR_RegMaxPayloadLength = 0x23, FSK_RegOsc = 0x24, LOR_RegHopPeriod = 0x24, FSK_RegPreambleMsb = 0x25, LOR_RegFifoRxByteAddr = 0x25, FSK_RegPreambleLsb = 0x26, LOR_RegModemConfig3 = 0x26, FSK_RegSyncConfig = 0x27, LOR_Reserved27 = 0x27, FSK_RegSyncValue1 = 0x28, LOR_RegFeiMsb = 0x28, FSK_RegSyncValue2 = 0x29, LOR_RegFeiMid = 0x29, FSK_RegSyncValue3 = 0x2a, LOR_RegFeiLsb = 0x2a, FSK_RegSyncValue4 = 0x2b, LOR_Reserved2b = 0x2b, FSK_RegSyncValue5 = 0x2c, LOR_RegRssiWideband = 0x2c, FSK_RegSyncValue6 = 0x2d, LOR_Reserved2d = 0x2d, FSK_RegSyncValue7 = 0x2e, LOR_Reserved2e = 0x2e, FSK_RegSyncValue8 = 0x2f, LOR_Reserved2f = 0x2f, FSK_RegPacketConfig1 = 0x30, LOR_Reserved30 = 0x30, FSK_RegPacketConfig2 = 0x31, LOR_RegDetectOptimize = 0x31, FSK_RegPayloadLength = 0x32, LOR_Reserved32 = 0x32, FSK_RegNodeAddr = 0x33, LOR_RegInvertIQ = 0x33, FSK_RegBroadcastAddr = 0x34, LOR_Reserved34 = 0x34, FSK_RegFifoThresh = 0x35, LOR_Reserved35 = 0x35, FSK_RegSeqConfig1 = 0x36, LOR_Reserved36 = 0x36, FSK_RegSeqConfig2 = 0x37, LOR_RegDetectionThreshold = 0x37, FSK_RegTimerResol = 0x38, LOR_Reserved38 = 0x38, FSK_RegTimer1Coeff = 0x39, LOR_RegSyncWord = 0x39, FSK_RegTimer2Coeff = 0x3a, LOR_Reserved3a = 0x3a, FSK_RegImageCal = 0x3b, LOR_Reserved3b = 0x3b, LOR_RegInvertIQ2 = 0x3b, FSK_RegTemp = 0x3c, LOR_Reserved3c = 0x3c, FSK_RegLowBat = 0x3d, LOR_Reserved3d = 0x3d, FSK_RegIrqFlags1 = 0x3e, LOR_Reserved3e = 0x3e, FSK_RegIrqFlags2 = 0x3f, LOR_Reserved3f = 0x3f, COM_RegDioMapping1 = 0x40, COM_RegDioMapping2 = 0x41, COM_RegVersion = 0x42, FSK_Reserved44 = 0x44, LOR_RegPllHop = 0x44, COM_RegTcxo = 0x4b, COM_RegPaDac = 0x4d, COM_RegFormerTemp = 0x5b, FSK_RegBitRateFrac = 0x5d, LOR_Reserved5d = 0x5d, COM_RegAgcRef = 0x61, COM_RegAgcThresh1 = 0x62, COM_RegAgcThresh2 = 0x63, COM_RegAgcThresh3 = 0x64, COM_RegPll = 0x70 } |

| enum | OPMODE_BITS_T { OPMODE_Mode0 = 0x01, OPMODE_Mode1 = 0x02, OPMODE_Mode2 = 0x04, _OPMODE_Mode_MASK = 7, _OPMODE_Mode_SHIFT = 0, OPMODE_LowFrequencyModeOn = 0x08, OPMODE_FSK_ModulationType0 = 0x20, OPMODE_FSK_ModulationType1 = 0x40, _OPMODE_FSK_ModulationType_MASK = 3, _OPMODE_FSK_ModulationType_SHIFT = 5, OPMODE_LOR_Reserved0x20 = 0x20, OPMODE_LOR_AccessSharedReg = 0x40, OPMODE_LongRangeMode = 0x80 } |

| enum | MODE_T { MODE_Sleep = 0, MODE_Standby = 1, MODE_FSTX = 2, MODE_TxMode = 3, MODE_FSRX = 4, MODE_FSK_RxMode = 5, MODE_LOR_RxContinuous = 5, MODE_FSK_Reserved6 = 6, MODE_LOR_RxSingle = 6, MODE_FSK_Reserved7 = 7, MODE_LOR_CAD = 7 } |

| enum | FSK_MODULATION_TYPE_T { MODULATION_FSK = 0, MODULATION_OOK = 1 } |

| enum | PACONFIG_BITS_T { PACONFIG_OutputPower0 = 0x01, PACONFIG_OutputPower1 = 0x02, PACONFIG_OutputPower2 = 0x04, PACONFIG_OutputPower3 = 0x08, _PACONFIG_OutputPower_MASK = 15, _PACONFIG_OutputPower_SHIFT = 0, PACONFIG_MaxPower0 = 0x10, PACONFIG_MaxPower1 = 0x20, PACONFIG_MaxPower2 = 0x40, _PACONFIG_MaxPower_MASK = 7, _PACONFIG_MaxPower_SHIFT = 4, PACONFIG_PaSelect = 0x80 } |

| enum | PARAMP_BITS_T { PARAMP_PaRamp0 = 0x01, PARAMP_PaRamp1 = 0x02, PARAMP_PaRamp2 = 0x04, PARAMP_PaRamp3 = 0x08, _PARAMP_PaRamp_MASK = 15, _PARAMP_PaRamp_SHIFT = 0, PARAMP_FSK_ModulationShaping0 = 0x20, PARAMP_FSK_ModulationShaping1 = 0x40, _PARAMP_FSK_ModulationShaping_MASK = 3, _PARAMP_FSK_ModulationShaping_SHIFT = 5 } |

| enum | PARAMP_T { PARAMP_3_4MS = 0, PARAMP_2MS = 1, PARAMP_1MS = 2, PARAMP_500US = 3, PARAMP_250US = 4, PARAMP_125US = 5, PARAMP_100US = 6, PARAMP_62US = 7, PARAMP_50US = 8, PARAMP_40US = 9, PARAMP_31US = 10, PARAMP_25US = 11, PARAMP_20US = 12, PARAMP_15US = 13, PARAMP_12US = 14, PARAMP_10US = 15 } |

| enum | MODSHAPING_T { MODSHAPING_NOSHAPING = 0, MODSHAPING_FSK_GaussianFilterBT1 = 1, MODSHAPING_FSK_GaussianFilterBT05 = 2, MODSHAPING_FSK_GaussianFilterBT03 = 3, MODSHAPING_OOK_FCutoffBitRate = 1, MODSHAPING_OOK_FCutoffBitRate2 = 2 } |

| enum | OCP_BITS_T { OCP_OcpTrim0 = 0x01, OCP_OcpTrim1 = 0x02, OCP_OcpTrim2 = 0x04, OCP_OcpTrim3 = 0x08, _OCP_OcpTrim_MASK = 15, _OCP_OcpTrim_SHIFT = 0, OCP_OcpOn = 0x10 } |

| enum | LNA_BITS_T { LNA_LnaBoostHf0 = 0x01, LNA_LnaBoostHf1 = 0x02, _LNA_LnaBoostHf_MASK = 3, _LNA_LnaBoostHf_SHIFT = 0, LNA_LnaBoostLf0 = 0x08, LNA_LnaBoostLf1 = 0x10, _LNA_LnaBoostLf_MASK = 3, _LNA_LnaBoostLf_SHIFT = 3, LNA_LnaGain0 = 0x20, LNA_LnaGain1 = 0x40, LNA_LnaGain2 = 0x80, _LNA_LnaGain_MASK = 7, _LNA_LnaGain_SHIFT = 5 } |

| enum | LNABOOSTHF_T { LNABOOSTHF_Default = 0, LNABOOSTHF_BoostOn = 3 } |

| enum | LNABOOSTLF_T { LNABOOSTLF_Default = 0 } |

| enum | LNAGAIN_T { LNAGAIN_G1 = 1, LNAGAIN_G2 = 2, LNAGAIN_G3 = 3, LNAGAIN_G4 = 4, LNAGAIN_G5 = 5, LNAGAIN_G6 = 6 } |

| enum | RXCONFIG_BITS_T { RXCONFIG_RxTrigger0 = 0x01, RXCONFIG_RxTrigger1 = 0x02, RXCONFIG_RxTrigger2 = 0x04, _RXCONFIG_RxTrigger_MASK = 7, _RXCONFIG_RxTrigger_SHIFT = 0, RXCONFIG_AgcAutoOn = 0x08, RXCONFIG_AfcAutoOn = 0x10, RXCONFIG_RestartRxWithPllLock = 0x20, RXCONFIG_RestartRxWithoutPllLock = 0x40, RXCONFIG_RestartRxOnCollision = 0x80 } |

| enum | RSSICONFIG_BITS_T { RSSICONFIG_RssiSmoothing0 = 0x01, RSSICONFIG_RssiSmoothing1 = 0x02, RSSICONFIG_RssiSmoothing2 = 0x04, _RSSICONFIG_RssiSmoothing_MASK = 7, _RSSICONFIG_RssiSmoothing_SHIFT = 0, RSSICONFIG_RssiOffset0 = 0x08, RSSICONFIG_RssiOffset1 = 0x10, RSSICONFIG_RssiOffset2 = 0x20, RSSICONFIG_RssiOffset3 = 0x40, RSSICONFIG_RssiOffset4 = 0x80, _RSSICONFIG_RssiOffset_MASK = 31, _RSSICONFIG_RssiOffset_SHIFT = 3 } |

| enum | RSSISMOOTHING_T { RSSISMOOTHING_2 = 0, RSSISMOOTHING_4 = 1, RSSISMOOTHING_8 = 2, RSSISMOOTHING_16 = 3, RSSISMOOTHING_32 = 4, RSSISMOOTHING_64 = 5, RSSISMOOTHING_128 = 6, RSSISMOOTHING_256 = 7 } |

| enum | LOR_IRQFLAG_BITS_T { LOR_IRQFLAG_CadDetected = 0x01, LOR_IRQFLAG_FhssChangeChannel = 0x02, LOR_IRQFLAG_CadDone = 0x04, LOR_IRQFLAG_TxDone = 0x08, LOR_IRQFLAG_ValidHeader = 0x10, LOR_IRQFLAG_PayloadCrcError = 0x20, LOR_IRQFLAG_RxDone = 0x40, LOR_IRQFLAG_RxTimeout = 0x80 } |

| enum | RXBW_BITS_T { RXBW_RxBwExp0 = 0x01, RXBW_RxBwExp1 = 0x02, RXBW_RxBwExp2 = 0x04, _RXBW_RxBwExp_MASK = 7, _RXBW_RxBwExp_SHIFT = 0, RXBW_RxBwMant0 = 0x08, RXBW_RxBwMant1 = 0x10, _RXBW_RxBwMant_MASK = 3, _RXBW_RxBwMant_SHIFT = 3 } |

| enum | RXBWMANT_T { RXBWMANT_0 = 0, RXBWMANT_1 = 1, RXBWMANT_2 = 2 } |

| enum | RXBWEXP_T { RXBWEXP_1 = 1, RXBWEXP_2 = 2, RXBWEXP_3 = 3, RXBWEXP_4 = 4, RXBWEXP_5 = 5, RXBWEXP_6 = 6, RXBWEXP_7 = 7 } |

| enum | OOKPEAK_BITS_T { OOKPEAK_OokPeakThreshStep0 = 0x01, OOKPEAK_OokPeakThreshStep1 = 0x02, OOKPEAK_OokPeakThreshStep2 = 0x04, _OOKPEAK_OokPeakThreshStep_MASK = 7, _OOKPEAK_OokPeakThreshStep_SHIFT = 0, OOKPEAK_OokThreshType0 = 0x08, OOKPEAK_OokThreshType1 = 0x10, _OOKPEAK_OokThreshType_MASK = 3, _OOKPEAK_OokThreshType_SHIFT = 3, OOKPEAK_BitSyncOn = 0x20 } |

| enum | OOKPEAKTHRESHSTEP_T { OOKPEAKTHRESHSTEP_05dB = 0, OOKPEAKTHRESHSTEP_1dB = 1, OOKPEAKTHRESHSTEP_15dB = 2, OOKPEAKTHRESHSTEP_2dB = 3, OOKPEAKTHRESHSTEP_3dB = 4, OOKPEAKTHRESHSTEP_4dB = 5, OOKPEAKTHRESHSTEP_5dB = 6, OOKPEAKTHRESHSTEP_6dB = 7 } |

| enum | OOKTHRESHTYPE_T { OOKTHRESHTYPE_FIXED = 0, OOKTHRESHTYPE_PEAK = 1, OOKTHRESHTYPE_AVERAGE = 2 } |

| enum | OOKAVG_BITS_T { OOKAVG_OokAvgThreshFilt0 = 0x01, OOKAVG_OokAvgThreshFilt1 = 0x02, _OOKAVG_OokAvgThreshFilt_MASK = 3, _OOKAVG_OokAvgThreshFilt_SHIFT = 0, OOKAVG_OokAvgOffset0 = 0x04, OOKAVG_OokAvgOffset1 = 0x08, _OOKAVG_OokAvgOffset_MASK = 3, _OOKAVG_OokAvgOffset_SHIFT = 2, OOKAVG_OokPeakThreshDec0 = 0x20, OOKAVG_OokPeakThreshDec1 = 0x40, OOKAVG_OokPeakThreshDec2 = 0x80, _OOKAVG_OokPeakThreshDec_MASK = 7, _OOKAVG_OokPeakThreshDec_SHIFT = 5 } |

| enum | OOKAVGTHRESHFILT_T { OOKAVGTHRESHFILT_32 = 0, OOKAVGTHRESHFILT_8 = 1, OOKAVGTHRESHFILT_4 = 2, OOKAVGTHRESHFILT_2 = 3 } |

| enum | OOKAVGOFFSET_T { OOKAVGOFFSET_0 = 0, OOKAVGOFFSET_2 = 1, OOKAVGOFFSET_4 = 2, OOKAVGOFFSET_6 = 3 } |

| enum | OOKPEAKTHRESHDEC_T { OOKPEAKTHRESHDEC_1_1 = 0, OOKPEAKTHRESHDEC_1_2 = 1, OOKPEAKTHRESHDEC_1_4 = 2, OOKPEAKTHRESHDEC_1_8 = 3, OOKPEAKTHRESHDEC_2_1 = 4, OOKPEAKTHRESHDEC_4_1 = 5, OOKPEAKTHRESHDEC_8_1 = 6, OOKPEAKTHRESHDEC_16_1 = 7 } |

| enum | MODEMSTAT_BITS_T { MODEMSTAT_SignalDetected = 0x01, MODEMSTAT_SignalSynchronized = 0x02, MODEMSTAT_RxOngoing = 0x04, MODEMSTAT_HeaderInfoValid = 0x08, MODEMSTAT_ModemClear = 0x10, MODEMSTAT_RxCodingRate0 = 0x20, MODEMSTAT_RxCodingRate1 = 0x40, MODEMSTAT_RxCodingRate2 = 0x80, _MODEMSTAT_RxCodingRate_MASK = 7, _MODEMSTAT_RxCodingRate_SHIFT = 5 } |

| enum | AFCFEI_BITS_T { AFCFEI_AfcAutoClearOn = 0x01, AFCFEI_AfcClear = 0x02, AFCFEI_AgcStart = 0x10 } |

| enum | HOPCHANNEL_BITS_T { HOPCHANNEL_FhssPresentChannel0 = 0x01, HOPCHANNEL_FhssPresentChannel1 = 0x02, HOPCHANNEL_FhssPresentChannel2 = 0x04, HOPCHANNEL_FhssPresentChannel3 = 0x08, HOPCHANNEL_FhssPresentChannel4 = 0x10, HOPCHANNEL_FhssPresentChannel5 = 0x20, _HOPCHANNEL_FhssPresentChannel_MASK = 63, _HOPCHANNEL_FhssPresentChannel_SHIFT = 0, HOPCHANNEL_CrcOnPayload = 0x40, HOPCHANNEL_PllTimeout = 0x80 } |

| enum | MODEMCONFIG1_BITS_T { MODEMCONFIG1_ImplicitHeaderModeOn = 0x01, MODEMCONFIG1_CodingRate0 = 0x02, MODEMCONFIG1_CodingRate1 = 0x04, MODEMCONFIG1_CodingRate2 = 0x08, _MODEMCONFIG1_CodingRate_MASK = 7, _MODEMCONFIG1_CodingRate_SHIFT = 0, MODEMCONFIG1_Bw0 = 0x10, MODEMCONFIG1_Bw1 = 0x20, MODEMCONFIG1_Bw2 = 0x40, MODEMCONFIG1_Bw3 = 0x80, _MODEMCONFIG1_Bw_MASK = 15, _MODEMCONFIG1_Bw_SHIFT = 4 } |

| enum | CODINGRATE_T { CODINGRATE_4_5 = 1, CODINGRATE_4_6 = 2, CODINGRATE_4_7 = 3, CODINGRATE_4_8 = 4 } |

| enum | BW_T { BW_7_8 = 0, BW_10_4 = 1, BW_15_6 = 2, BW_20_8 = 3, BW_31_25 = 4, BW_41_7 = 5, BW_62_5 = 6, BW_125 = 7, BW_250 = 8, BW_500 = 9 } |

| enum | MODEMCONFIG2_BITS_T { MODEMCONFIG2_SymbTimeoutMsb0 = 0x01, MODEMCONFIG2_SymbTimeoutMsb1 = 0x02, _MODEMCONFIG2_SymbTimeoutMsb_MASK = 3, _MODEMCONFIG2_SymbTimeoutMsb_SHIFT = 0, MODEMCONFIG2_RxPayloadCrcOn = 0x04, MODEMCONFIG2_TxContinuousMode = 0x08, MODEMCONFIG2_SpreadingFactor0 = 0x10, MODEMCONFIG2_SpreadingFactor1 = 0x20, MODEMCONFIG2_SpreadingFactor2 = 0x40, MODEMCONFIG2_SpreadingFactor3 = 0x80, _MODEMCONFIG2_SpreadingFactor_MASK = 15, _MODEMCONFIG2_SpreadingFactor_SHIFT = 4 } |

| enum | SPREADINGFACTOR_T { SPREADINGFACTOR_64 = 6, SPREADINGFACTOR_128 = 7, SPREADINGFACTOR_256 = 8, SPREADINGFACTOR_512 = 9, SPREADINGFACTOR_1024 = 10, SPREADINGFACTOR_2048 = 11, SPREADINGFACTOR_4096 = 12 } |

| enum | PREAMBLEDETECT_BITS_T { PREABLEDETECT_PreambleDetectorTol0 = 0x01, PREABLEDETECT_PreambleDetectorTol1 = 0x02, PREABLEDETECT_PreambleDetectorTol2 = 0x04, PREABLEDETECT_PreambleDetectorTol3 = 0x08, PREABLEDETECT_PreambleDetectorTol4 = 0x10, _PREABLEDETECT_PreambleDetectorTol4_MASK = 31, _PREABLEDETECT_PreambleDetectorTol4_SHIFT = 0, PREABLEDETECT_PreambleDetectorSize0 = 0x20, PREABLEDETECT_PreambleDetectorSize1 = 0x40, _PREABLEDETECT_PreambleDetectorSize_MASK = 3, _PREABLEDETECT_PreambleDetectorSize_SHIFT = 5, PREABLEDETECT_PreambleDetectorOn = 0x80 } |

| enum | PREAMBLEDETECTORSIZE_T { PREAMBLEDETECTORSIZE_1 = 0, PREAMBLEDETECTORSIZE_2 = 1, PREAMBLEDETECTORSIZE_3 = 2 } |

| enum | OSC_BITS_T { OSC_ClkOut0 = 0x01, OSC_ClkOut1 = 0x02, OSC_ClkOut2 = 0x04, _OSC_ClkOut_MASK = 7, _OSC_ClkOut_SHIFT = 0, OSC_RcCalStart = 0x08 } |

| enum | CLKOUT_T { CLKOUT_1 = 0, CLKOUT_2 = 1, CLKOUT_4 = 2, CLKOUT_8 = 3, CLKOUT_16 = 4, CLKOUT_32 = 5, CLKOUT_RC = 6, CLKOUT_OFF = 7 } |

| enum | MODEMCONFIG3_BITS_T { MODEMCONFIG3_AgcAutoOn = 0x04, MODEMCONFIG3_LowDataRateOptimize = 0x08 } |

| enum | SYNCCONFIG_BITS_T { SYNCCONFIG_SyncSize0 = 0x01, SYNCCONFIG_SyncSize1 = 0x02, SYNCCONFIG_SyncSize2 = 0x04, _SYNCCONFIG_SyncSize_MASK = 7, _SYNCCONFIG_SyncSize_SHIFT = 0, SYNCCONFIG_SyncOn = 0x10, SYNCCONFIG_PreamblePolarity = 0x20, SYNCCONFIG_AutoRestartMode0 = 0x40, SYNCCONFIG_AutoRestartMode1 = 0x80, _SYNCCONFIG_AutoRestartMode_MASK = 3, _SYNCCONFIG_AutoRestartMode_SHIFT = 6 } |

| enum | AUTORESTARTMODE_T { AUTORESTARTMODE_OFF = 0, AUTORESTARTMODE_ON_NOPLL = 1, AUTORESTARTMODE_ON_PLL = 2 } |

| enum | FEIMSB_BITS_T { FEIMSB_FreqError0 = 0x01, FEIMSB_FreqError1 = 0x02, FEIMSB_FreqError2 = 0x04, FEIMSB_FreqError3 = 0x08, _FEIMSB_FreqError_MASK = 15, _FEIMSB_FreqError_SHIFT = 0 } |

| enum | PACKETCONFIG1_BITS_T { PACKETCONFIG1_CrcWhiteningType = 0x01, PACKETCONFIG1_AddressFiltering0 = 0x02, PACKETCONFIG1_AddressFiltering1 = 0x04, _PACKETCONFIG1_AddressFiltering_MASK = 3, _PACKETCONFIG1_AddressFiltering_SHIFT = 1, PACKETCONFIG1_CrcAutoClearOff = 0x08, PACKETCONFIG1_CrcOn = 0x10, PACKETCONFIG1_DcFree0 = 0x20, PACKETCONFIG1_DcFree1 = 0x40, _PACKETCONFIG1_DcFree_MASK = 3, _PACKETCONFIG1_DcFree_SHIFT = 5, PACKETCONFIG1_PacketFormat = 0x80 } |

| enum | ADDRESSFILTERING_T { ADDRESSFILTERING_NONE = 0, ADDRESSFILTERING_NODE = 1, ADDRESSFILTERING_NODE_BROADCAST = 2 } |

| enum | DCFREE_T { DCFREE_NONE = 0, DCFREE_MANCHESTER = 1, DCFREE_WHITENING = 2 } |

| enum | PACKETCONFIG2_BITS_T { PACKETCONFIG2_PayloadLengthMsb0 = 0x01, PACKETCONFIG2_PayloadLengthMsb1 = 0x02, PACKETCONFIG2_PayloadLengthMsb2 = 0x04, _PACKETCONFIG2_PayloadLengthMsb_MASK = 7, _PACKETCONFIG2_PayloadLengthMsb_SHIFT = 0, PACKETCONFIG2_BeaconOn = 0x08, PACKETCONFIG2_IoHomeOn = 0x20, PACKETCONFIG2_DataMode = 0x40 } |

| enum | DETECTOPTIMIZE_BITS_T { DETECTOPTIMIZE_DetectionOptimize0 = 0x01, DETECTOPTIMIZE_DetectionOptimize1 = 0x02, DETECTOPTIMIZE_DetectionOptimize2 = 0x04, _DETECTOPTIMIZE_DetectionOptimize_MASK = 7, _DETECTOPTIMIZE_DetectionOptimize_SHIFT = 0 } |

| enum | DETECTIONOPTIMIZE_T { DETECTIONOPTIMIZE_SF7_SF12 = 3, DETECTIONOPTIMIZE_SF6 = 5 } |

| enum | INVERTIQ_BITS_T { INVERTIQ_InvertIQTxOff = 0x01, INVERTIQ_InvertIQRx = 0x40 } |

| enum | FIFOTHRESH_BITS_T { FIFOTHRESH_FifoThreshold0 = 0x01, FIFOTHRESH_FifoThreshold1 = 0x02, FIFOTHRESH_FifoThreshold2 = 0x04, FIFOTHRESH_FifoThreshold3 = 0x08, FIFOTHRESH_FifoThreshold4 = 0x10, FIFOTHRESH_FifoThreshold5 = 0x20, _FIFOTHRESH_FifoThreshold_MASK = 63, _FIFOTHRESH_FifoThreshold_SHIFT = 0, FIFOTHRESH_TxStartCondition = 0x80 } |

| enum | SEQCONFIG1_BITS_T { SEQCONFIG1_FromTransit = 0x01, SEQCONFIG1_FromIdle = 0x02, SEQCONFIG1_LowPowerSelection = 0x04, SEQCONFIG1_FromStart0 = 0x08, SEQCONFIG1_FromStart1 = 0x10, _SEQCONFIG1_FromStart_MASK = 3, _SEQCONFIG1_FromStart_SHIFT = 3, SEQCONFIG1_IdleMode = 0x20, SEQCONFIG1_SequencerStop = 0x40, SEQCONFIG1_SequencerStart = 0x80 } |

| enum | FROMSTART_T { FROMSTART_ToLowPowerSelection = 0, FROMSTART_ToReceiveState = 1, FROMSTART_ToTransmitState = 2, FROMSTART_ToTransmitStateOnFifoLevel = 3 } |

| enum | SEQCONFIG2_BITS_T { SEQCONFIG2_FromPacketReceived0 = 0x01, SEQCONFIG2_FromPacketReceived1 = 0x02, SEQCONFIG2_FromPacketReceived2 = 0x04, _SEQCONFIG2_FromPacketReceived_MASK = 7, _SEQCONFIG2_FromPacketReceived_SHIFT = 0, SEQCONFIG2_FromRxTimeout0 = 0x08, SEQCONFIG2_FromRxTimeout1 = 0x10, _SEQCONFIG2_FromRxTimeout_MASK = 3, _SEQCONFIG2_FromRxTimeout_SHIFT = 3, SEQCONFIG2_FromReceive0 = 0x20, SEQCONFIG2_FromReceive1 = 0x40, SEQCONFIG2_FromReceive2 = 0x80, _SEQCONFIG2_FromReceive_MASK = 3, _SEQCONFIG2_FromReceive_SHIFT = 5 } |

| enum | FROMPACKETRECEIVED_T { FROMPACKETRECEIVED_ToSequencerOff = 0, FROMPACKETRECEIVED_ToTransmitStateOnFifoEmpty = 1, FROMPACKETRECEIVED_ToLowPowerSelection = 2, FROMPACKETRECEIVED_ToReceiveViaFS = 3, FROMPACKETRECEIVED_ToReceive = 4 } |

| enum | FROMRXTIMEOUT_T { FROMRXTIMEOUT_ToReceiveViaReceiveStart = 0, FROMRXTIMEOUT_ToTransmitState = 1, FROMRXTIMEOUT_ToLowPowerSelection = 2, FROMRXTIMEOUT_ToSequencerOffState = 3 } |

| enum | FROMRECEIVE_T { FROMRECEIVE_ToPcketReceived = 1, FROMRECEIVE_ToLowPowerSelection = 2, FROMRECEIVE_ToPacketReceived = 3, FROMRECEIVE_ToSequencerOffOnRSSI = 4, FROMRECEIVE_ToSequencerOffOnSync = 5, FROMRECEIVE_ToSequencerOffOnPreambleDetect = 6 } |

| enum | TIMERRESOL_BITS_T { TIMERRESOL_Timer2Resolution0 = 0x01, TIMERRESOL_Timer2Resolution1 = 0x02, _TIMERRESOL_Timer2Resolution_MASK = 3, _TIMERRESOL_Timer2Resolution_SHIFT = 0, TIMERRESOL_Timer1Resolution0 = 0x04, TIMERRESOL_Timer1Resolution1 = 0x08, _TIMERRESOL_Timer1Resolution_MASK = 3, _TIMERRESOL_Timer1Resolution_SHIFT = 2 } |

| enum | TIMERRESOLUTION_T { TIMERRESOLUTION_DISABLED = 0, TIMERRESOLUTION_64us = 1, TIMERRESOLUTION_4_1ms = 2, TIMERRESOLUTION_262ms = 3 } |

| enum | IMAGECAL_BITS_T { IMAGECAL_TempMonitorOff = 0x01, IMAGECAL_TempThreshold0 = 0x02, IMAGECAL_TempThreshold1 = 0x04, _IMAGECAL_TempThreshold_MASK = 3, _IMAGECAL_TempThreshold_SHIFT = 1, IMAGECAL_TenpChange = 0x08, IMAGECAL_ImageCalRunning = 0x20, IMAGECAL_ImageCalStart = 0x40, IMAGECAL_AutoImageCalOn = 0x80 } |

| enum | TEMPTHRESHOLD_T { TEMPTHRESHOLD_5C = 0, TEMPTHRESHOLD_10C = 1, TEMPTHRESHOLD_15C = 2, TEMPTHRESHOLD_20C = 3 } |

| enum | LOWBAT_BITS_T { LOWBAT_LowBatTrim0 = 0x01, LOWBAT_LowBatTrim1 = 0x02, LOWBAT_LowBatTrim2 = 0x04, _LOWBAT_LowBatTrim_MASK = 7, _LOWBAT_LowBatTrim_SHIFT = 0, LOWBAT_LowBatOn = 0x08 } |

| enum | LOWBATTRIM_T { LOWBATTRIM_1_695 = 0, LOWBATTRIM_1_764 = 1, LOWBATTRIM_1_835 = 2, LOWBATTRIM_1_905 = 3, LOWBATTRIM_1_976 = 4, LOWBATTRIM_2_045 = 5, LOWBATTRIM_2_116 = 6, LOWBATTRIM_2_185 = 7 } |

| enum | IRQFLAGS1_BITS_T { IRQFLAGS1_SyncAddressMatch = 0x01, IRQFLAGS1_PreambleDetect = 0x02, IRQFLAGS1_Timeout = 0x04, IRQFLAGS1_Rssi = 0x08, IRQFLAGS1_PllLock = 0x10, IRQFLAGS1_TxReady = 0x20, IRQFLAGS1_RxReady = 0x40, IRQFLAGS1_ModeReady = 0x80 } |

| enum | IRQFLAGS2_BITS_T { IRQFLAGS2_LowBat = 0x01, IRQFLAGS2_CrcOk = 0x02, IRQFLAGS2_PayloadReady = 0x04, IRQFLAGS2_PacketSent = 0x08, IRQFLAGS2_FifoOverrun = 0x10, IRQFLAGS2_FifoLevel = 0x20, IRQFLAGS2_FifoEmpty = 0x40, IRQFLAGS2_FifoFull = 0x80 } |

| enum | DIOMAPPING1_BITS_T { DOIMAPPING1_Dio3Mapping0 = 0x01, DOIMAPPING1_Dio3Mapping1 = 0x02, DOIMAPPING1_Dio3Mapping_MASK = 3, DOIMAPPING1_Dio3Mapping_SHIFT = 0, DOIMAPPING1_Dio2Mapping0 = 0x04, DOIMAPPING1_Dio2Mapping1 = 0x08, DOIMAPPING1_Dio2Mapping_MASK = 3, DOIMAPPING1_Dio2Mapping_SHIFT = 2, DOIMAPPING1_Dio1Mapping0 = 0x10, DOIMAPPING1_Dio1Mapping1 = 0x20, DOIMAPPING1_Dio1Mapping_MASK = 3, DOIMAPPING1_Dio1Mapping_SHIFT = 4, DOIMAPPING1_Dio0Mapping0 = 0x40, DOIMAPPING1_Dio0Mapping1 = 0x80, DOIMAPPING1_Dio0Mapping_MASK = 3, DOIMAPPING1_Dio0Mapping_SHIFT = 6 } |

| enum | DIOMAPPING2_BITS_T { DOIMAPPING2_MapPreambleDetect = 0x01, DOIMAPPING2_Dio5Mapping0 = 0x10, DOIMAPPING2_Dio5Mapping1 = 0x20, DOIMAPPING2_Dio5Mapping_MASK = 3, DOIMAPPING2_Dio5Mapping_SHIFT = 4, DOIMAPPING2_Dio4Mapping0 = 0x40, DOIMAPPING2_Dio4Mapping1 = 0x80, DOIMAPPING2_Dio4Mapping_MASK = 3, DOIMAPPING2_Dio4Mapping_SHIFT = 6 } |

| enum | DIOMAPPING_T { DIOMAPPING_00 = 0, DIOMAPPING_01 = 1, DIOMAPPING_10 = 2, DIOMAPPING_11 = 3 } |

| enum | PLLHOP_BITS_T { PLLHOP_FastHopOn = 0x80 } |

| enum | TCXO_BITS_T { TCXO_TcxoOn = 0x10 } |

| enum | PADAC_BITS_T { PADAC_PaDac0 = 0x01, PADAC_PaDac1 = 0x02, PADAC_PaDac2 = 0x04, _PADAC_PaDac_MASK = 7, _PADAC_PaDac_SHIFT = 0 } |

| enum | PADAC_T { PADAC_DEFAULT = 4, PADAC_BOOST = 7 } |

| enum | BITRATEFRAC_BITS_T { BITRATEFRAC_BitRateFrac0 = 0x01, BITRATEFRAC_BitRateFrac1 = 0x02, BITRATEFRAC_BitRateFrac2 = 0x04, BITRATEFRAC_BitRateFrac3 = 0x08, _BITRATEFRAC_BitRateFrac_MASK = 15, _BITRATEFRAC_BitRateFrac_SHIFT = 0 } |

| enum | ACFREF_BITS_T { AGCREF_AgcReferenceLevel0 = 0x01, AGCREF_AgcReferenceLevel1 = 0x02, AGCREF_AgcReferenceLevel2 = 0x04, AGCREF_AgcReferenceLevel3 = 0x08, AGCREF_AgcReferenceLevel4 = 0x10, AGCREF_AgcReferenceLevel5 = 0x20, _AGCREF_AgcReferenceLevel_MASK = 63, _AGCREF_AgcReferenceLevel_SHIFT = 0 } |

| enum | ACGTHRESH1_BITS_T { AGCTHRESH1_AcgStep10 = 0x01, AGCTHRESH1_AcgStep11 = 0x02, AGCTHRESH1_AcgStep12 = 0x04, AGCTHRESH1_AcgStep13 = 0x08, _AGCTHRESH1_AcgStep1_MASK = 15, _AGCTHRESH1_AcgStep1_SHIFT = 0 } |

| enum | ACGTHRESH2_BITS_T { AGCTHRESH2_AcgStep30 = 0x01, AGCTHRESH2_AcgStep31 = 0x02, AGCTHRESH2_AcgStep32 = 0x04, AGCTHRESH2_AcgStep33 = 0x08, _AGCTHRESH2_AcgStep3_MASK = 15, _AGCTHRESH2_AcgStep3_SHIFT = 0, AGCTHRESH2_AcgStep20 = 0x10, AGCTHRESH2_AcgStep21 = 0x20, AGCTHRESH2_AcgStep22 = 0x40, AGCTHRESH2_AcgStep23 = 0x80, _AGCTHRESH2_AcgStep2_MASK = 15, _AGCTHRESH2_AcgStep2_SHIFT = 4 } |

| enum | LOR_DETECTIONTHRESHOLD_T { LOR_DetectionThreshold_SF7_SF12 = 0x0a, LOR_DetectionThreshold_SF6 = 0x0c } |

| enum | ACGTHRESH3_BITS_T { AGCTHRESH3_AcgStep50 = 0x01, AGCTHRESH3_AcgStep51 = 0x02, AGCTHRESH3_AcgStep52 = 0x04, AGCTHRESH3_AcgStep53 = 0x08, _AGCTHRESH3_AcgStep5_MASK = 15, _AGCTHRESH3_AcgStep5_SHIFT = 0, AGCTHRESH3_AcgStep40 = 0x10, AGCTHRESH3_AcgStep41 = 0x20, AGCTHRESH3_AcgStep42 = 0x40, AGCTHRESH3_AcgStep43 = 0x80, _AGCTHRESH3_AcgStep4_MASK = 15, _AGCTHRESH3_AcgStep4_SHIFT = 4 } |

Public Member Functions | |

| SX1276 (uint8_t chipRev=chipRevision, int bus=1, int cs=10, int resetPin=14, int dio0=2, int dio1=3, int dio2=4, int dio3=5, int dio4=17, int dio5=9) | |

| ~SX1276 () | |

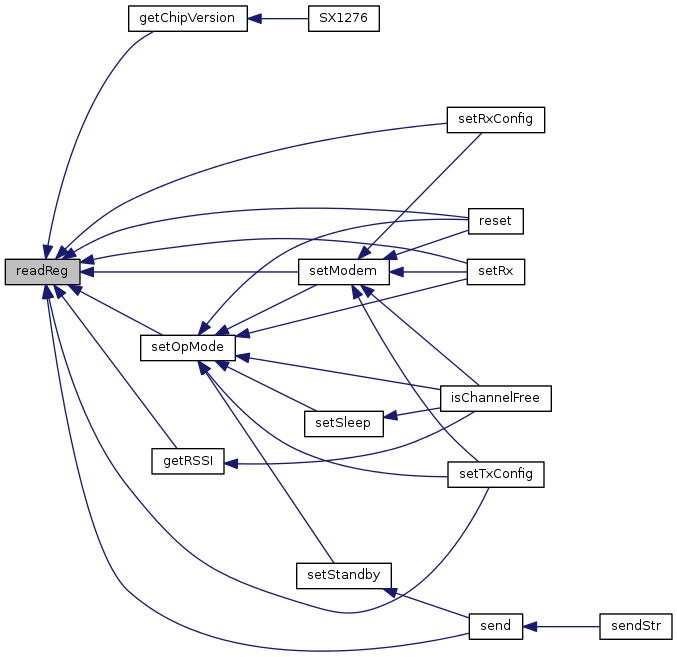

| uint8_t | readReg (uint8_t reg) |

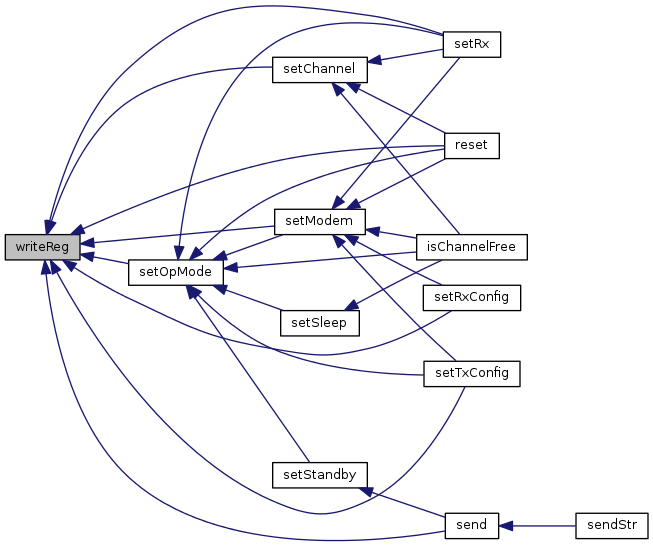

| bool | writeReg (uint8_t reg, uint8_t val) |

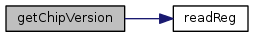

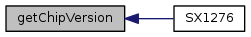

| uint8_t | getChipVersion () |

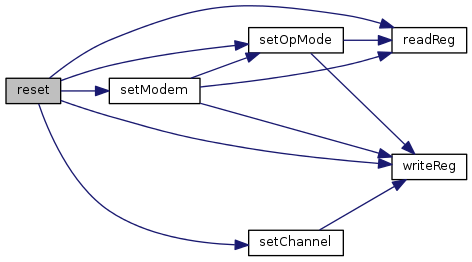

| void | reset () |

| void | readFifo (uint8_t *buffer, int len) |

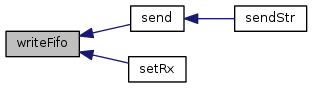

| void | writeFifo (uint8_t *buffer, int len) |

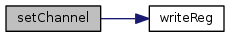

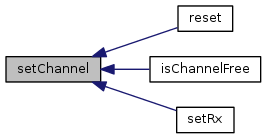

| void | setChannel (uint32_t freq) |

| void | setOpMode (MODE_T opMode) |

| void | setModem (RADIO_MODEM_T modem) |

| void | setSleep () |

| void | setStandby () |

| int16_t | getRSSI (RADIO_MODEM_T modem) |

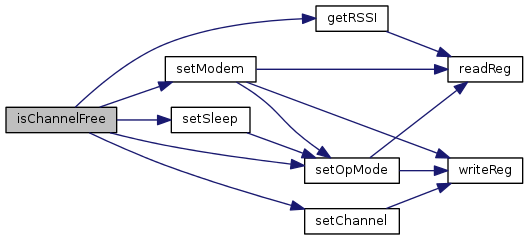

| bool | isChannelFree (RADIO_MODEM_T modem, uint32_t freq, int16_t rssiThresh) |

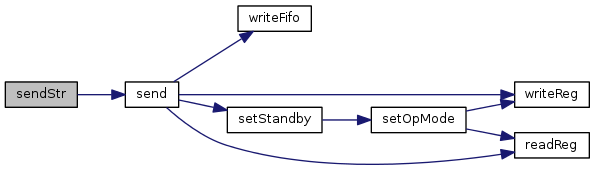

| RADIO_EVENT_T | sendStr (std::string buffer, int timeout) |

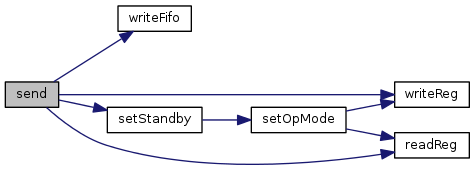

| RADIO_EVENT_T | send (uint8_t *buffer, uint8_t size, int timeout) |

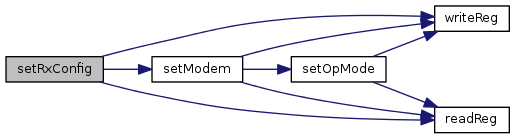

| void | setRxConfig (RADIO_MODEM_T modem, uint32_t bandwidth, uint32_t datarate, uint8_t coderate, uint32_t bandwidthAfc, uint16_t preambleLen, uint16_t symbTimeout, bool fixLen, uint8_t payloadLen, bool crcOn, bool freqHopOn, uint8_t hopPeriod, bool iqInverted, bool rxContinuous) |

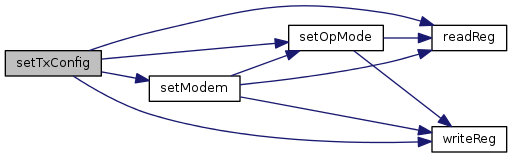

| void | setTxConfig (RADIO_MODEM_T modem, int8_t power, uint32_t fdev, uint32_t bandwidth, uint32_t datarate, uint8_t coderate, uint16_t preambleLen, bool fixLen, bool crcOn, bool freqHopOn, uint8_t hopPeriod, bool iqInverted) |

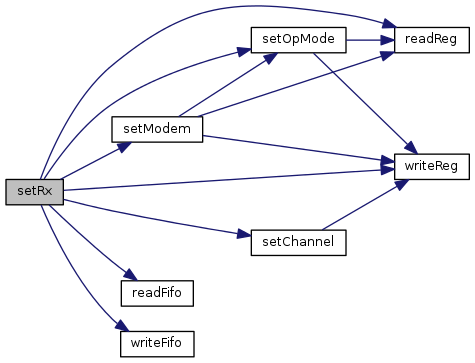

| RADIO_EVENT_T | setRx (uint32_t timeout) |

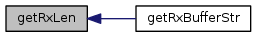

| std::string | getRxBufferStr () |

| uint8_t * | getRxBuffer () |

| int | getRxRSSI () |

| int | getRxSNR () |

| int | getRxLen () |

Protected Types | |

| enum | RADIO_STATES_T { STATE_IDLE = 0, STATE_RX_RUNNING, STATE_TX_RUNNING, STATE_CAD } |

Protected Member Functions | |

| void | rxChainCalibration () |

| void | init () |

| RADIO_EVENT_T | setTx (int timeout) |

| void | startCAD () |

| void | setMaxPayloadLength (RADIO_MODEM_T modem, uint8_t max) |

| void | csOn () |

| void | csOff () |

Static Protected Attributes | |

| static const uint8_t | m_writeMode = 0x80 |

| enum RADIO_MODEM_T |

What modem we are configured for

| enum RADIO_EVENT_T |

Events that can occurr during a TX or RX operation.

When sending or receiving a packet (calling setTx()/send() or setRx()), the state will be initialized to ESTATE_EXEC to indicate the operation is in progress. Once an event has occurred, this state will be updated accordingly.

For receiving, if RX_DONE is set, then it is safe to retrieve the rx buffer (via getRxBuffer()/getRxBufferStr()) as well as query the RSSI and SNR. On RX_ERROR, these values will be the same as they were last set during the last RX_DONE event.

| enum SX1276_REGS_T |

SX1276 registers

NOTE: reserved registers must not be written into or read from. Reserved bitfields must always be 0.

This device has a set of "common" registers, as well as registers that represent different things depending on whether the device in in LoRa mode or FSK/OOK mode. So here, we will prefix the register names with COM (common), LOR (LoRa mode), and FSK (FSK/OOK mode) accordingly.

| enum OPMODE_BITS_T |

OpMode register (differing bitfields depending on mode)

| enum MODE_T |

Mode values

FSK_ModulationType values

| enum PACONFIG_BITS_T |

RegPaConfig register

| enum PARAMP_BITS_T |

RegPaRamp register

| enum PARAMP_T |

PARAMP_PaRamp values

| enum MODSHAPING_T |

PARAMP_ModulationShaping values. Note, these mean different things depending on whether you are using FSK or OOK. Hence the FSK/OOK dups. We will also name these as 'MODSHAPING_', rather than the lengthy 'MODULATIONSHAPING... '

| enum OCP_BITS_T |

RegOcp register (see datasheet for OcpTrim values)

| enum LNA_BITS_T |

Lna register

| enum LNABOOSTHF_T |

LnaBoostHf values

| enum LNABOOSTLF_T |

LnaBoostLf values

| enum LNAGAIN_T |

LnaGain values

| enum RXCONFIG_BITS_T |

FSK_RxConfig register. See Table 24 in the data sheet for the meanings of the RxTrigger values.

| enum RSSICONFIG_BITS_T |

FSK_RssiConfig register

| enum RSSISMOOTHING_T |

RssiSmoothing values

| enum LOR_IRQFLAG_BITS_T |

LOR_RegIrqFlagsMask and LOR_RegIrqFlags registers

| enum RXBW_BITS_T |

FSK_RxBw register and FSK_RegAfcBw registers

| enum RXBWMANT_T |

RXBW_RxBwMant values

| enum RXBWEXP_T |

RXBW_RxBwExp values

| enum OOKPEAK_BITS_T |

FSK_OokPeak register

| enum OOKPEAKTHRESHSTEP_T |

OokPeakThreshStep values

| enum OOKTHRESHTYPE_T |

OokPeakThreshType values

| enum OOKAVG_BITS_T |

FSK_OokAvg register

| enum OOKAVGTHRESHFILT_T |

OokAvgThreshFilt values

| enum OOKAVGOFFSET_T |

OokAvgOffset values

| enum OOKPEAKTHRESHDEC_T |

OokPeakThreshDec values

| enum MODEMSTAT_BITS_T |

LOR_ModemStat register

| enum AFCFEI_BITS_T |

FSK_RegAfcFei register

| enum HOPCHANNEL_BITS_T |

LOR_HopChannel register

| enum MODEMCONFIG1_BITS_T |

LOR_ModemConfig1 register

| enum CODINGRATE_T |

CodingRate values

| enum BW_T |

Bw values

| enum MODEMCONFIG2_BITS_T |

LOR_ModemConfig2 register

| enum SPREADINGFACTOR_T |

SpreadingFactor values (expressed as a base-2 logarithm)

FSK_PreableDetect register

PreambleDetectorSize values

| enum OSC_BITS_T |

FSK_Osc register

| enum CLKOUT_T |

ClkOut values

| enum MODEMCONFIG3_BITS_T |

LOR_ModemConfig3 register

| enum SYNCCONFIG_BITS_T |

FSK_SyncConfig register

| enum AUTORESTARTMODE_T |

AutoRestartMode values

| enum FEIMSB_BITS_T |

LOR_FeiMsb register (4 bit MSB of Fei value)

| enum PACKETCONFIG1_BITS_T |

FSK_PacketConfig1 register

| enum ADDRESSFILTERING_T |

AddressFiltering values

| enum DCFREE_T |

DcFree values (DC-free encoding/decoding schemes)

| enum PACKETCONFIG2_BITS_T |

FSK_PacketConfig2 register

LOR_DetectOptimize register

| enum DETECTIONOPTIMIZE_T |

DetectionOptimize values

| enum INVERTIQ_BITS_T |

LOR_InvertIQ register

| enum FIFOTHRESH_BITS_T |

FSK_FifoThresh register

| enum SEQCONFIG1_BITS_T |

FSK_SeqConfig1 register

| enum FROMSTART_T |

FromStart values

| enum SEQCONFIG2_BITS_T |

FSK_SeqConfig2 register

| enum FROMPACKETRECEIVED_T |

FromPacketReceived values

| enum FROMRXTIMEOUT_T |

FromRxTimeout values

| enum FROMRECEIVE_T |

FromReceive values

| enum TIMERRESOL_BITS_T |

FSK_TimerResol register

| enum TIMERRESOLUTION_T |

Timer1/Timer2Resolution values

| enum IMAGECAL_BITS_T |

FSK_ImageCal register

| enum TEMPTHRESHOLD_T |

TempThreshold values

| enum LOWBAT_BITS_T |

FSK_LowBat register

| enum LOWBATTRIM_T |

LowBatTrim values

| enum IRQFLAGS1_BITS_T |

FSK_IrqFlags1 register

| enum IRQFLAGS2_BITS_T |

FSK_IrqFlags2 register

| enum DIOMAPPING1_BITS_T |

COM_DioMapping1 register. See Tables 18, 29, and 30 in the datasheet for the different mappings depending on mode.

| enum DIOMAPPING2_BITS_T |

COM_DioMapping2 register. See Tables 18, 29, and 30 in the datasheet for the different mappings depending on mode.

| enum DIOMAPPING_T |

DioXMapping values

These differ depending on LoRa, FSK packet, and FSK continous modes. See Tables 29, 30 (FSK), and 18 (LoRa) in the datasheet for details.

| enum PLLHOP_BITS_T |

LOR_PllHop (or FSK_PllHop depending on who you believe) register

| enum TCXO_BITS_T |

COM_Tcxo register

| enum PADAC_BITS_T |

COM_PaDac register

| enum PADAC_T |

PaDac values

| enum BITRATEFRAC_BITS_T |

FSK_BitRateFrac register

| enum ACFREF_BITS_T |

COM_AgcRef register

These registers have 2 sets of values depending on whether LowFrequencyModeOn is set or unset.

| enum ACGTHRESH1_BITS_T |

COM_AgcThresh1 register

These registers have 2 sets of values depending on whether LowFrequencyModeOn is set or unset.

| enum ACGTHRESH2_BITS_T |

COM_AgcThresh2 register

These registers have 2 sets of values depending on whether LowFrequencyModeOn is set or unset.

LOR_RegDetectionThreshold values

| enum ACGTHRESH3_BITS_T |

COM_AgcThresh3 register

These registers have 2 sets of values depending on whether LowFrequencyModeOn is set or unset.

|

protected |

What internal state are we in

| SX1276 | ( | uint8_t | chipRev = chipRevision, |

| int | bus = 1, |

||

| int | cs = 10, |

||

| int | resetPin = 14, |

||

| int | dio0 = 2, |

||

| int | dio1 = 3, |

||

| int | dio2 = 4, |

||

| int | dio3 = 5, |

||

| int | dio4 = 17, |

||

| int | dio5 = 9 |

||

| ) |

SX1276 constructor

Since this is a shield, you will not have much choice as to what pins are used.

| chipRev | chip revision, default is 0x12 |

| bus | spi bus to use |

| cs | GPIO pin to use as SPI Chip Select |

| resetPin | GPIO pin to use as reset (A0=GPIO14) |

| dio0 | GPIO pin to use as reset DIO0 intr |

| dio1 | GPIO pin to use as reset DIO1 intr |

| dio2 | GPIO pin to use as reset DIO2 intr |

| dio3 | GPIO pin to use as reset DIO3 intr |

| dio4 | GPIO pin to use as reset DIO4 intr |

| dio5 | GPIO pin to use as reset DIO5 intr |

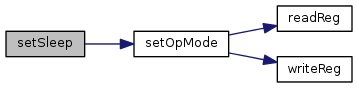

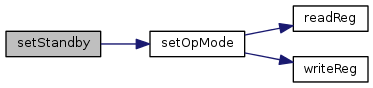

| uint8_t readReg | ( | uint8_t | reg | ) |

read a register

| reg | the register to read |

| bool writeReg | ( | uint8_t | reg, |

| uint8_t | val | ||

| ) |

write to a register

| reg | the register to write to |

| val | the value to write |

| uint8_t getChipVersion | ( | ) |

return the chip revision

| void reset | ( | ) |

reset the modem

| void readFifo | ( | uint8_t * | buffer, |

| int | len | ||

| ) |

read the FIFO into a buffer

| buffer | The buffer to read data into |

| len | The length of the buffer |

| void writeFifo | ( | uint8_t * | buffer, |

| int | len | ||

| ) |

write a buffer into the FIFO

| buffer | The buffer containing the data to write |

| len | The length of the buffer |

| void setChannel | ( | uint32_t | freq | ) |

Set the frequency to transmit and receive on

| freq | The frequency to set |

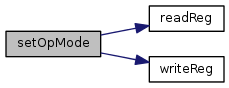

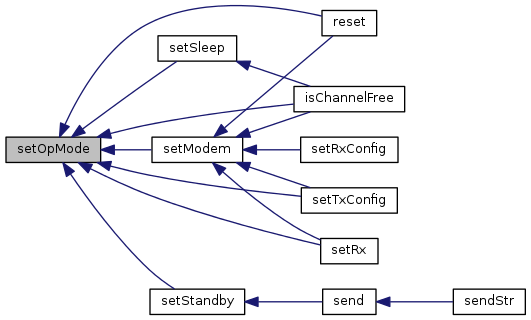

| void setOpMode | ( | MODE_T | opMode | ) |

Set the operating mode

| opMode | One of the MODE_T values |

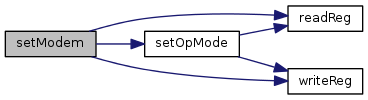

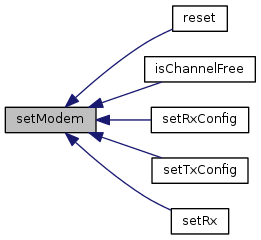

| void setModem | ( | RADIO_MODEM_T | modem | ) |

Set the modem to access. This can be either the LORA or KSK/OOK modem.

| modem | One of the MODEM_T values |

| void setSleep | ( | ) |

Place the SX1276 into sleep mode

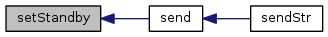

| void setStandby | ( | void | ) |

Place the SX1276 into standby mode

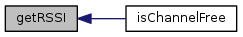

| int16_t getRSSI | ( | RADIO_MODEM_T | modem | ) |

Return the current Received Signal Strength Indicator for the given modem

| modem | One of the MODEM_T values |

| bool isChannelFree | ( | RADIO_MODEM_T | modem, |

| uint32_t | freq, | ||

| int16_t | rssiThresh | ||

| ) |

Check to see if a given channel is free by comparing the RSSI to the supplied threshold.

| modem | One of the MODEM_T values |

| freq | The channel to check |

| rssiThresh | The RSSI threshold, over which the channel os considerd in use. |

| SX1276::RADIO_EVENT_T sendStr | ( | std::string | buffer, |

| int | timeout | ||

| ) |

Send the supplied string. This writes the string into the FIFO and places the modem in transmit mode (via setTx()). This is a wrapper around send().

| buffer | The buffer to send |

| timeout | The timeout in milliseconds |

| SX1276::RADIO_EVENT_T send | ( | uint8_t * | buffer, |

| uint8_t | size, | ||

| int | timeout | ||

| ) |

Send the supplied buffer. The writes the buffer into the FIFO and places the modem in transmit mode (via setTx()).

| buffer | The buffer to send |

| size | The size of the buffer |

| timeout | The timeout in milliseconds |

| void setRxConfig | ( | RADIO_MODEM_T | modem, |

| uint32_t | bandwidth, | ||

| uint32_t | datarate, | ||

| uint8_t | coderate, | ||

| uint32_t | bandwidthAfc, | ||

| uint16_t | preambleLen, | ||

| uint16_t | symbTimeout, | ||

| bool | fixLen, | ||

| uint8_t | payloadLen, | ||

| bool | crcOn, | ||

| bool | freqHopOn, | ||

| uint8_t | hopPeriod, | ||

| bool | iqInverted, | ||

| bool | rxContinuous | ||

| ) |

Set the receive configuration for a modem. It is important that both the receive and transmit configurations match in order for communication to work between two radios.

| modem | One of the MODEM_T values |

| bandwidth | The bandwidth to use. Valid values are FSK : >= 2600 and <= 250000 Hz LoRa: [125 kHz, 250 kHz, 500 kHz] |

| datarate | Sets the Datarate FSK : 600..300000 bits/s LoRa: [6: 64, 7: 128, 8: 256, 9: 512, 10: 1024, 11: 2048, 12: 4096 chips] |

| coderate | Sets the coding rate (LoRa only) FSK : N/A ( set to 0 ) LoRa: [1: 4/5, 2: 4/6, 3: 4/7, 4: 4/8] |

| bandwidthAfc | Sets the AFC Bandwidth (FSK only) FSK : >= 2600 and <= 250000 Hz LoRa: N/A ( set to 0 ) |

| preambleLen | Sets the Preamble length FSK : Number of bytes LoRa: Length in symbols (the hardware adds 4 more symbols) |

| symbTimeout | Sets the RxSingle timeout value (LoRa only) FSK : N/A ( set to 0 ) LoRa: timeout in symbols |

| fixLen | Fixed length packets [false: variable, true: fixed] |

| payloadLen | Sets payload length when fixed length is used |

| crcOn | Enables/Disables the CRC [false: OFF, true: ON] |

| freqHopOn | Enables disables the intra-packet frequency hopping FSK : N/A ( set to 0 ) LoRa: [false: OFF, true: ON] |

| hopPeriod | Number of symbols bewteen each hop FSK : N/A ( set to 0 ) LoRa: Number of symbols |

| iqInverted | Inverts IQ signals (LoRa only) FSK : N/A ( set to 0 ) LoRa: [false: not inverted, true: inverted] |

| rxContinuous | Sets the reception in continuous mode [false: single mode, true: continuous mode] |

| void setTxConfig | ( | RADIO_MODEM_T | modem, |

| int8_t | power, | ||

| uint32_t | fdev, | ||

| uint32_t | bandwidth, | ||

| uint32_t | datarate, | ||

| uint8_t | coderate, | ||

| uint16_t | preambleLen, | ||

| bool | fixLen, | ||

| bool | crcOn, | ||

| bool | freqHopOn, | ||

| uint8_t | hopPeriod, | ||

| bool | iqInverted | ||

| ) |

Set the transmit configuration for a modem. It is important that both the receive and transmit configurations match in order for communication to work between two radios.

| modem | One of the MODEM_T values |

| power | Sets the output power [dBm] |

| fdev | Sets the frequency deviation (FSK only) FSK : [Hz] LoRa: 0 |

| bandwidth | Sets the bandwidth (LoRa only) FSK : 0 LoRa: [125 kHz, 250 kHz, or 500 kHz] |

| datarate | Sets the Datarate FSK : 600..300000 bits/s LoRa: [6: 64, 7: 128, 8: 256, 9: 512, 10: 1024, 11: 2048, 12: 4096 chips] |

| coderate | Sets the coding rate (LoRa only) FSK : N/A ( set to 0 ) LoRa: [1: 4/5, 2: 4/6, 3: 4/7, 4: 4/8] |

| preambleLen | Sets the preamble length FSK : Number of bytes LoRa: Length in symbols (the hardware adds 4 more symbols) |

| fixLen | Fixed length packets [false: variable, true: fixed] |

| crcOn | Enables disables the CRC [false: OFF, true: ON] |

| freqHopOn | Enables disables the intra-packet frequency hopping FSK : N/A ( set to 0 ) LoRa: [false: OFF, true: ON] |

| hopPeriod | Number of symbols bewteen each hop FSK : N/A ( set to 0 ) LoRa: Number of symbols |

| iqInverted | Inverts IQ signals (LoRa only) FSK : N/A ( set to 0 ) LoRa: [false: not inverted, true: inverted] |

| SX1276::RADIO_EVENT_T setRx | ( | uint32_t | timeout | ) |

Start a receive operation. The method will return when completed, either successfully, or in error (crc, or other issue). If completed successfully, the returned buffer can be read via getRxBuffer() or getRxBufferStr(). In addition, values for RSSI and SNR (Lora only) can be retrieved.

| timeout | The timeout in milliseconds |

|

inline |

Upon a successful receive, this method can be used to retrieve the received packet.

|

inline |

Upon a successful receive, this method can be used to retrieve the received packet.

|

inline |

Upon a successful receive, this method can be used to retrieve the received packet's Received Signal Strength Indicator (RSSI) value.

|

inline |

Upon a successful receive, this method can be used to retrieve the received packet's Signal to Noise (SNR) value.

|

inline |

Upon a successful receive, this method can be used to retrieve the number of bytes received.

1.8.11

1.8.11