|

upm

0.4.0

Sensor/Actuator repository for libmraa (v0.8.0)

|

|

upm

0.4.0

Sensor/Actuator repository for libmraa (v0.8.0)

|

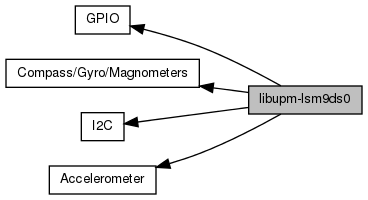

LSM9DS0 accelerometer library. More...

Data Structures | |

| class | LSM9DS0 |

| API for the LSM9DS0 3-axis Gyroscope, Accelerometer, and Magnetometer. More... | |

Enumerations | |

| enum | REG_G_T { REG_WHO_AM_I_G = 0x0f, REG_CTRL_REG1_G = 0x20, REG_CTRL_REG2_G = 0x21, REG_CTRL_REG3_G = 0x22, REG_CTRL_REG4_G = 0x23, REG_CTRL_REG5_G = 0x24, REG_REFERENCE_G = 0x25, REG_STATUS_REG_G = 0x27, REG_OUT_X_L_G = 0x28, REG_OUT_X_H_G = 0x29, REG_OUT_Y_L_G = 0x2a, REG_OUT_Y_H_G = 0x2b, REG_OUT_Z_L_G = 0x2c, REG_OUT_Z_H_G = 0x2d, REG_FIFO_CTRL_REG_G = 0x2e, REG_FIFO_SRC_REG_G = 0x2f, REG_INT1_CFG_G = 0x30, REG_INT1_SRC_G = 0x31, REG_INT1_TSH_XH_G = 0x32, REG_INT1_TSH_XL_G = 0x33, REG_INT1_TSH_YH_G = 0x34, REG_INT1_TSH_YL_G = 0x35, REG_INT1_TSH_ZH_G = 0x36, REG_INT1_TSH_ZL_G = 0x37, REG_INT1_DURATION_G = 0x38 } |

| enum | CTRL_REG1_G_BITS_T { CTRL_REG1_G_YEN = 0x01, CTRL_REG1_G_XEN = 0x02, CTRL_REG1_G_ZEN = 0x04, CTRL_REG1_G_PD = 0x08, CTRL_REG1_G_BW0 = 0x10, CTRL_REG1_G_BW1 = 0x20, _CTRL_REG1_G_BW_MASK = 3, _CTRL_REG1_G_BW_SHIFT = 4, CTRL_REG1_G_DR0 = 0x40, CTRL_REG1_G_DR1 = 0x80, _CTRL_REG1_G_DR_MASK = 3, _CTRL_REG1_G_DR_SHIFT = 6, CTRL_REG1_G_ODR0 = 0x10, CTRL_REG1_G_ODR1 = 0x20, CTRL_REG1_G_ODR2 = 0x40, CTRL_REG1_G_ODR3 = 0x80, _CTRL_REG1_G_ODR_MASK = 15, _CTRL_REG1_G_ODR_SHIFT = 4 } |

| enum | G_ODR_T { G_ODR_95_12_5 = 0, G_ODR_95_25 = 1, G_ODR_190_12_5 = 4, G_ODR_190_25 = 5, G_ODR_190_50 = 6, G_ODR_190_70 = 7, G_ODR_380_20 = 8, G_ODR_380_25 = 9, G_ODR_380_50 = 10, G_ODR_380_100 = 11, G_ODR_760_30 = 12, G_ODR_760_35 = 13, G_ODR_760_50 = 14, G_ODR_760_100 = 15 } |

| enum | CTRL_REG2_G_BITS_T { CTRL_REG2_G_HPCF0 = 0x01, CTRL_REG2_G_HPCF1 = 0x02, CTRL_REG2_G_HPCF2 = 0x04, CTRL_REG2_G_HPCF3 = 0x08, _CTRL_REG2_G_HPCF_MASK = 15, _CTRL_REG2_G_HPCF_SHIFT = 0, CTRL_REG2_G_HPM0 = 0x10, CTRL_REG2_G_HPM1 = 0x20, _CTRL_REG2_G_HPM_MASK = 3, _CTRL_REG2_G_HPM_SHIFT = 4 } |

| enum | G_HPCF_T { G_HPCF_7_2 = 0, G_HPCF_3_5 = 1, G_HPCF_1_8 = 2, G_HPCF_0_9 = 3, G_HPCF_0_45 = 4, G_HPCF_0_18 = 5, G_HPCF_0_09 = 6, G_HPCF_0_045 = 7, G_HPCF_0_018 = 8, G_HPCF_0_009 = 9 } |

| enum | G_HPM_T { G_HPM_NORMAL_RESET_HPF = 0, G_HPM_REFERENCE = 1, G_HPM_NORMAL = 2, G_HPM_AUTORESET_ON_INTR = 3 } |

| enum | CTRL_REG3_G_BITS_T { CTRL_REG3_G_I2_EMPTY = 0x01, CTRL_REG3_G_I2_ORUN = 0x02, CTRL_REG3_G_I2_WTM = 0x04, CTRL_REG3_G_I2_DRDY = 0x08, CTRL_REG3_G_PP_OD = 0x10, CTRL_REG3_G_H_LACTIVE = 0x20, CTRL_REG3_G_I1_BOOT = 0x40, CTRL_REG3_G_I1_INT1 = 0x80 } |

| enum | CTRL_REG4_G_BITS_T { CTRL_REG4_G_SIM = 0x01, CTRL_REG4_G_ST0 = 0x02, CTRL_REG4_G_ST1 = 0x04, _CTRL_REG4_G_ST_MASK = 3, _CTRL_REG4_G_ST_SHIFT = 1, CTRL_REG4_G_FS0 = 0x10, CTRL_REG4_G_FS1 = 0x20, _CTRL_REG4_G_FS_MASK = 3, _CTRL_REG4_G_FS_SHIFT = 4, CTRL_REG4_G_BLE = 0x40, CTRL_REG4_G_BDU = 0x80 } |

| enum | G_ST_T { G_ST_NORMAL = 0, G_ST_SELFTEST0 = 1, G_ST_SELFTEST1 = 3 } |

| enum | G_FS_T { G_FS_245 = 0, G_FS_500 = 1, G_FS_2000 = 2 } |

| enum | CTRL_REG5_G_BITS_T { CTRL_REG5_G_OUTSEL0 = 0x01, CTRL_REG5_G_OUTSEL1 = 0x02, _CTRL_REG5_G_OUTSEL_MASK = 3, _CTRL_REG5_G_OUTSEL_SHIFT = 0, CTRL_REG5_G_INT1SEL0 = 0x04, CTRL_REG5_G_INT1SEL1 = 0x08, _CTRL_REG5_G_INT1SEL_MASK = 3, _CTRL_REG5_G_INT1SEL_SHIFT = 2, CTRL_REG5_G_HPEN = 0x10, CTRL_REG5_G_FIFO_EN = 0x40, CTRL_REG5_G_BOOT = 0x80 } |

| enum | G_INT1OUTSEL_T { G_INT1OUTSEL_0 = 0, G_INT1OUTSEL_1 = 1, G_INT1OUTSEL_2 = 2, G_INT1OUTSEL_3 = 3 } |

| enum | STATUS_REG_G_BITS_T { STATUS_REG_G_XDA = 0x01, STATUS_REG_G_YDA = 0x02, STATUS_REG_G_ZDA = 0x04, STATUS_REG_G_ZYXDA = 0x08, STATUS_REG_G_XOR = 0x10, STATUS_REG_G_YOR = 0x20, STATUS_REG_G_ZOR = 0x40, STATUS_REG_G_ZYXOR = 0x80 } |

| enum | FIFO_CTRL_REG_G_T { FIFO_CTRL_REG_G_WTM0 = 0x01, FIFO_CTRL_REG_G_WTM1 = 0x02, FIFO_CTRL_REG_G_WTM2 = 0x04, FIFO_CTRL_REG_G_WTM3 = 0x08, FIFO_CTRL_REG_G_WTM4 = 0x10, _FIFO_CTRL_REG_G_WTM_MASK = 31, _FIFO_CTRL_REG_G_WTM_SHIFT = 0, FIFO_CTRL_REG_G_FM0 = 0x20, FIFO_CTRL_REG_G_FM1 = 0x40, FIFO_CTRL_REG_G_FM2 = 0x80, _FIFO_CTRL_REG_G_FM_MASK = 7, _FIFO_CTRL_REG_G_FM_SHIFT = 5 } |

| enum | G_FM_T { G_FM_BYPASS = 0, G_FM_FIFO = 1, G_FM_STREAM = 2, G_FM_STREAM2FIFO = 3, G_FM_BYPASS2STREAM = 4 } |

| enum | FIFO_SRC_REG_G_BITS_T { FIFO_CTRL_REG_G_FSS0 = 0x01, FIFO_CTRL_REG_G_FSS1 = 0x02, FIFO_CTRL_REG_G_FSS2 = 0x04, FIFO_CTRL_REG_G_FSS3 = 0x08, FIFO_CTRL_REG_G_FSS4 = 0x10, _FIFO_CTRL_REG_G_FSS_MASK = 31, _FIFO_CTRL_REG_G_FSS_SHIFT = 0, FIFO_CTRL_REG_G_EMPTY = 0x20, FIFO_CTRL_REG_G_OVRN = 0x40, FIFO_CTRL_REG_G_WTM = 0x80 } |

| enum | INT1_CFG_G_BITS_T { INT1_CFG_G_XLIE = 0x01, INT1_CFG_G_XHIE = 0x02, INT1_CFG_G_YLIE = 0x04, INT1_CFG_G_YHIE = 0x08, INT1_CFG_G_ZLIE = 0x10, INT1_CFG_G_ZHIE = 0x20, INT1_CFG_G_LIR = 0x40, INT1_CFG_G_ANDOR = 0x80 } |

| enum | INT1_SRC_G_BITS_T { INT1_SRC_G_XL = 0x01, INT1_SRC_G_XH = 0x02, INT1_SRC_G_YL = 0x04, INT1_SRC_G_YH = 0x08, INT1_SRC_G_ZL = 0x10, INT1_SRC_G_ZH = 0x20, INT1_SRC_G_IA = 0x40 } |

| enum | REG_XM_T { REG_OUT_TEMP_L_XM = 0x05, REG_OUT_TEMP_H_XM = 0x06, REG_STATUS_REG_M = 0x07, REG_OUT_X_L_M = 0x08, REG_OUT_X_H_M = 0x09, REG_OUT_Y_L_M = 0x0a, REG_OUT_Y_H_M = 0x0b, REG_OUT_Z_L_M = 0x0c, REG_OUT_Z_H_M = 0x0d, REG_WHO_AM_I_XM = 0x0f, REG_INT_CTRL_REG_M = 0x12, REG_INT_SRC_REG_M = 0x13, REG_INT_THS_L_M = 0x14, REG_INT_THS_H_M = 0x15, REG_OFFSET_X_L_M = 0x16, REG_OFFSET_X_H_M = 0x17, REG_OFFSET_Y_L_M = 0x18, REG_OFFSET_Y_H_M = 0x19, REG_OFFSET_Z_L_M = 0x1a, REG_OFFSET_Z_H_M = 0x1b, REG_REFERENCE_X = 0x1c, REG_REFERENCE_Y = 0x1d, REG_REFERENCE_Z = 0x1e, REG_CTRL_REG0_XM = 0x1f, REG_CTRL_REG1_XM = 0x20, REG_CTRL_REG2_XM = 0x21, REG_CTRL_REG3_XM = 0x22, REG_CTRL_REG4_XM = 0x23, REG_CTRL_REG5_XM = 0x24, REG_CTRL_REG6_XM = 0x25, REG_CTRL_REG7_XM = 0x26, REG_STATUS_REG_A = 0x27, REG_OUT_X_L_A = 0x28, REG_OUT_X_H_A = 0x29, REG_OUT_Y_L_A = 0x2a, REG_OUT_Y_H_A = 0x2b, REG_OUT_Z_L_A = 0x2c, REG_OUT_Z_H_A = 0x2d, REG_FIFO_CTRL_REG = 0x2e, REG_FIFO_SRC_REG = 0x2f, REG_INT_GEN_1_REG = 0x30, REG_INT_GEN_1_SRC = 0x31, REG_INT_GEN_1_THS = 0x32, REG_INT_GEN_1_DURATION = 0x33, REG_INT_GEN_2_REG = 0x34, REG_INT_GEN_2_SRC = 0x35, REG_INT_GEN_2_THS = 0x36, REG_INT_GEN_2_DURATION = 0x37, REG_CLICK_CFG = 0x38, REG_CLICK_SRC = 0x39, REG_CLICK_THS = 0x3a, REG_TIME_LIMIT = 0x3b, REG_TIME_LATENCY = 0x3c, REG_TIME_WINDOW = 0x3d, REG_ACT_THS = 0x3e, REG_ACT_DUR = 0x3f } |

| enum | STATUS_REG_M_BITS_T { STATUS_REG_M_XMDA = 0x01, STATUS_REG_M_YMDA = 0x02, STATUS_REG_M_ZMDA = 0x04, STATUS_REG_M_ZYXMDA = 0x08, STATUS_REG_M_XMOR = 0x10, STATUS_REG_M_YMOR = 0x20, STATUS_REG_M_ZMOR = 0x40, STATUS_REG_M_ZYXMOR = 0x80 } |

| enum | INT_CTRL_REG_M_BITS_T { INT_CTRL_REG_M_MIEN = 0x01, INT_CTRL_REG_M_4D = 0x02, INT_CTRL_REG_M_IEL = 0x04, INT_CTRL_REG_M_IEA = 0x08, INT_CTRL_REG_M_PP_OD = 0x10, INT_CTRL_REG_M_ZMIEN = 0x20, INT_CTRL_REG_M_YMIEN = 0x40, INT_CTRL_REG_M_XMIEN = 0x80 } |

| enum | INT_SRC_REG_M_BITS_T { INT_SRC_REG_M_MINT = 0x01, INT_SRC_REG_M_MROI = 0x02, INT_SRC_REG_M_NTH_Z = 0x04, INT_SRC_REG_M_NTH_Y = 0x08, INT_SRC_REG_M_NTH_X = 0x10, INT_SRC_REG_M_PTH_Z = 0x20, INT_SRC_REG_M_PTH_Y = 0x40, INT_SRC_REG_M_PTH_X = 0x80 } |

| enum | CTRL_REG0_XM_BITS_T { CTRL_REG0_XM_HPIS2 = 0x01, CTRL_REG0_XM_HPIS1 = 0x02, CTRL_REG0_XM_HP_CLICK = 0x04, CTRL_REG0_XM_WTM_LEN = 0x20, CTRL_REG0_XM_FIFO_EN = 0x40, CTRL_REG0_XM_BOOT = 0x80 } |

| enum | CTRL_REG1_XM_BITS_T { CTRL_REG1_XM_AXEN = 0x01, CTRL_REG1_XM_AYEN = 0x02, CTRL_REG1_XM_AZEN = 0x03, CTRL_REG1_XM_BDU = 0x04, CTRL_REG1_XM_AODR0 = 0x10, CTRL_REG1_XM_AODR1 = 0x20, CTRL_REG1_XM_AODR2 = 0x40, CTRL_REG1_XM_AODR3 = 0x80, _CTRL_REG1_XM_AODR_MASK = 15, _CTRL_REG1_XM_AODR_SHIFT = 4 } |

| enum | XM_AODR_T { XM_AODR_PWRDWN = 0, XM_AODR_3_125 = 1, XM_AODR_6_25 = 2, XM_AODR_12_5 = 3, XM_AODR_25 = 4, XM_AODR_50 = 5, XM_AODR_100 = 6, XM_AODR_200 = 7, XM_AODR_400 = 8, XM_AODR_800 = 9, XM_AODR_1000 = 10 } |

| enum | CTRL_REG2_XM_BITS_T { CTRL_REG2_XM_SIM = 0x01, CTRL_REG2_XM_AST0 = 0x02, CTRL_REG2_XM_AST1 = 0x04, _CTRL_REG2_XM_AST_MASK = 3, _CTRL_REG2_XM_AST_SHIFT = 1, CTRL_REG2_XM_AFS0 = 0x08, CTRL_REG2_XM_AFS1 = 0x10, CTRL_REG2_XM_AFS2 = 0x20, _CTRL_REG2_XM_AFS_MASK = 7, _CTRL_REG2_XM_AFS_SHIFT = 3, CTRL_REG2_XM_ABW0 = 0x40, CTRL_REG2_XM_ABW1 = 0x80, _CTRL_REG2_XM_ABW_MASK = 3, _CTRL_REG2_XM_ABW_SHIFT = 6 } |

| enum | XM_AST_T { XM_AST_NORMAL = 0, XM_AST_POS_SIGN = 1, XM_AST_NEG_SIGN = 2 } |

| enum | XM_AFS_T { XM_AFS_2 = 0, XM_AFS_4 = 1, XM_AFS_6 = 2, XM_AFS_8 = 3, XM_AFS_16 = 4 } |

| enum | XM_ABW_T { XM_ABW_773 = 0, XM_ABW_194 = 1, XM_ABW_362 = 2, XM_ABW_50 = 3 } |

| enum | CTRL_REG3_XM_BITS_T { CTRL_REG3_XM_P1_EMPTY = 0x01, CTRL_REG3_XM_P1_DRDYM = 0x02, CTRL_REG3_XM_P1_DRDYA = 0x04, CTRL_REG3_XM_P1_INTM = 0x08, CTRL_REG3_XM_P1_INT2 = 0x10, CTRL_REG3_XM_P1_INT1 = 0x20, CTRL_REG3_XM_P1_TAP = 0x40, CTRL_REG3_XM_P1_BOOT = 0x80 } |

| enum | CTRL_REG4_XM_BITS_T { CTRL_REG4_XM_P2_WTM = 0x01, CTRL_REG4_XM_P2_OVERRUN = 0x02, CTRL_REG4_XM_P2_DRDYM = 0x04, CTRL_REG4_XM_P2_DRDYA = 0x08, CTRL_REG4_XM_P2_INTM = 0x10, CTRL_REG4_XM_P2_INT2 = 0x20, CTRL_REG4_XM_P2_INT1 = 0x40, CTRL_REG4_XM_P2_TAP = 0x80 } |

| enum | CTRL_REG5_XM_BITS_T { CTRL_REG5_XM_LIR1 = 0x01, CTRL_REG5_XM_LIR2 = 0x02, CTRL_REG5_XM_ODR0 = 0x04, CTRL_REG5_XM_ODR1 = 0x08, CTRL_REG5_XM_ODR2 = 0x10, _CTRL_REG5_XM_ODR_MASK = 7, _CTRL_REG5_XM_ODR_SHIFT = 2, CTRL_REG5_XM_RES0 = 0x20, CTRL_REG5_XM_RES1 = 0x40, _CTRL_REG5_XM_RES_MASK = 3, _CTRL_REG5_XM_RES_SHIFT = 5, CTRL_REG5_XM_TEMP_EN = 0x80 } |

| enum | XM_ODR_T { XM_ODR_3_125 = 0, XM_ODR_6_25 = 1, XM_ODR_12_5 = 2, XM_ODR_25 = 3, XM_ODR_50 = 4, XM_ODR_100 = 5 } |

| enum | XM_RES_T { XM_RES_LOW = 0, XM_RES_HIGH = 3 } |

| enum | CTRL_REG6_XM_BITS_T { CTRL_REG6_XM_MFS0 = 0x20, CTRL_REG6_XM_MFS1 = 0x40, _CTRL_REG6_XM_MFS_MASK = 3, _CTRL_REG6_XM_MFS_SHIFT = 5 } |

| enum | XM_MFS_T { XM_MFS_2 = 0, XM_MFS_4 = 1, XM_MFS_8 = 2, XM_MFS_12 = 3 } |

| enum | CTRL_REG7_XM_BITS_T { CTRL_REG7_XM_MD0 = 0x01, CTRL_REG7_XM_MD1 = 0x02, _CTRL_REG7_XM_MD_MASK = 3, _CTRL_REG7_XM_MD_SHIFT = 0, CTRL_REG7_XM_MLP = 0x04, CTRL_REG7_XM_AFDS = 0x20, CTRL_REG7_XM_AHPM0 = 0x40, CTRL_REG7_XM_AHPM1 = 0x80, _CTRL_REG7_XM_AHPM_MASK = 3, _CTRL_REG7_XM_AHPM_SHIFT = 6 } |

| enum | XM_MD_T { XM_MD_CONTINUOUS = 0, XM_MD_SINGLE = 1, XM_MD_POWERDOWN = 2 } |

| enum | XM_AHPM_T { XM_AHPM_NORMAL_REF = 0, XM_AHPM_REFERENCE = 1, XM_AHPM_NORMAL = 2, XM_AHPM_AUTORESET = 3 } |

| enum | STATUS_REG_A_BITS_T { STATUS_REG_A_XADA = 0x01, STATUS_REG_A_YADA = 0x02, STATUS_REG_A_ZADA = 0x04, STATUS_REG_A_ZYXADA = 0x08, STATUS_REG_A_XAOR = 0x10, STATUS_REG_A_YAOR = 0x20, STATUS_REG_A_ZAOR = 0x40, STATUS_REG_A_ZYXAOR = 0x80 } |

| enum | FIFO_CTRL_REG_T { FIFO_CTRL_REG_FTH0 = 0x01, FIFO_CTRL_REG_FTH1 = 0x02, FIFO_CTRL_REG_FTH2 = 0x04, FIFO_CTRL_REG_FTH3 = 0x08, FIFO_CTRL_REG_FTH4 = 0x10, _FIFO_CTRL_REG_FTH_MASK = 31, _FIFO_CTRL_REG_FTH_SHIFT = 0, FIFO_CTRL_REG_FM0 = 0x20, FIFO_CTRL_REG_FM1 = 0x40, FIFO_CTRL_REG_FM2 = 0x80, _FIFO_CTRL_REG_FM_MASK = 7, _FIFO_CTRL_REG_FM_SHIFT = 5 } |

| enum | FM_T { FM_BYPASS = 0, FM_FIFO = 1, FM_STREAM = 2, FM_STREAM2FIFO = 3, FM_BYPASS2STREAM = 4 } |

| enum | FIFO_SRC_REG_BITS_T { FIFO_CTRL_REG_FSS0 = 0x01, FIFO_CTRL_REG_FSS1 = 0x02, FIFO_CTRL_REG_FSS2 = 0x04, FIFO_CTRL_REG_FSS3 = 0x08, FIFO_CTRL_REG_FSS4 = 0x10, _FIFO_CTRL_REG_FSS_MASK = 31, _FIFO_CTRL_REG_FSS_SHIFT = 0, FIFO_CTRL_REG_EMPTY = 0x20, FIFO_CTRL_REG_OVRN = 0x40, FIFO_CTRL_REG_WTM = 0x80 } |

| enum | INT_GEN_X_REG_BITS_T { INT_GEN_X_REG_XLIE_XDOWNE = 0x01, INT_GEN_X_REG_XHIE_XUPE = 0x02, INT_GEN_X_REG_YLIE_YDOWNE = 0x04, INT_GEN_X_REG_YHIE_YUPE = 0x08, INT_GEN_X_REG_ZLIE_ZDOWNE = 0x10, INT_GEN_X_REG_ZHIE_ZUPE = 0x20, INT_GEN_X_REG_6D = 0x40, INT_GEN_X_REG_AOI = 0x80 } |

| enum | INT_GEN_X_SRC_BITS_T { INT_GEN_X_SRC_XL = 0x01, INT_GEN_X_SRC_XH = 0x02, INT_GEN_X_SRC_YL = 0x04, INT_GEN_X_SRC_YH = 0x08, INT_GEN_X_SRC_ZL = 0x10, INT_GEN_X_SRC_ZH = 0x20, INT_GEN_X_SRC_IA = 0x40 } |

| enum | INT_GEN_X_THS_BITS_T { INT_GEN_X_THS0 = 0x01, INT_GEN_X_THS1 = 0x02, INT_GEN_X_THS2 = 0x04, INT_GEN_X_THS3 = 0x08, INT_GEN_X_THS4 = 0x10, INT_GEN_X_THS5 = 0x20, INT_GEN_X_THS6 = 0x40, _INT_GEN_X_THS_MASK = 127, _INT_GEN_X_THS_SHIFT = 0 } |

| enum | INT_GEN_X_DUR_BITS_T { INT_GEN_X_DUR0 = 0x01, INT_GEN_X_DUR1 = 0x02, INT_GEN_X_DUR2 = 0x04, INT_GEN_X_DUR3 = 0x08, INT_GEN_X_DUR4 = 0x10, INT_GEN_X_DUR5 = 0x20, INT_GEN_X_DUR6 = 0x40, _INT_GEN_X_DUR_MASK = 127, _INT_GEN_X_DUR_SHIFT = 0 } |

| enum | CLICK_CONFIG_BITS_T { CLICK_CONFIG_XS = 0x01, CLICK_CONFIG_XD = 0x02, CLICK_CONFIG_YS = 0x04, CLICK_CONFIG_YD = 0x08, CLICK_CONFIG_ZS = 0x10, CLICK_CONFIG_ZD = 0x20 } |

| enum | CLICK_SRC_BITS_T { CLICK_SRC_X = 0x01, CLICK_SRC_Y = 0x02, CLICK_SRC_Z = 0x04, CLICK_SRC_SIGN = 0x08, CLICK_SRC_SCLICK = 0x10, CLICK_SRC_DCLICK = 0x20, CLICK_SRC_IA = 0x40 } |

| enum | CLICK_THS_BITS_T { CLICK_THS_THS0 = 0x01, CLICK_THS_THS1 = 0x02, CLICK_THS_THS2 = 0x04, CLICK_THS_THS3 = 0x08, CLICK_THS_THS4 = 0x10, CLICK_THS_THS5 = 0x20, CLICK_THS_THS6 = 0x40, _CLICK_THS_THS_MASK = 127, _CLICK_THS_THS_SHIFT = 0 } |

| enum | CLICK_TIME_LIMIT_BITS_T { CLICK_TIME_LIMIT_TLI0 = 0x01, CLICK_TIME_LIMIT_TLI1 = 0x02, CLICK_TIME_LIMIT_TLI2 = 0x04, CLICK_TIME_LIMIT_TLI3 = 0x08, CLICK_TIME_LIMIT_TLI4 = 0x10, CLICK_TIME_LIMIT_TLI5 = 0x20, CLICK_TIME_LIMIT_TLI6 = 0x40, _CLICK_TIME_LIMIT_TLI_MASK = 127, _CLICK_TIME_LIMIT_TLI_SHIFT = 0 } |

| enum | ACT_THS_BITS_T { ACT_THS_ACTH0 = 0x01, ACT_THS_ACTH1 = 0x02, ACT_THS_ACTH2 = 0x04, ACT_THS_ACTH3 = 0x08, ACT_THS_ACTH4 = 0x10, ACT_THS_ACTH5 = 0x20, ACT_THS_ACTH6 = 0x40, _ACT_THS_ACTH_MASK = 127, _ACT_THS_ACTH_SHIFT = 0 } |

| enum | DEVICE_T { DEV_GYRO, DEV_XM } |

| enum | INTERRUPT_PINS_T { INTERRUPT_G_INT, INTERRUPT_G_DRDY, INTERRUPT_XM_GEN1, INTERRUPT_XM_GEN2 } |

| enum REG_G_T |

LSM9DS0 Gyroscope (G) registers

| enum CTRL_REG1_G_BITS_T |

Gyro CTRL_REG1_G bits

| enum G_ODR_T |

CRTL_REG1_G_ODR values

| enum CTRL_REG2_G_BITS_T |

Gyro CTRL_REG2_G bits

| enum G_HPCF_T |

CRTL_REG2_G_HPCF values

See table 26 in the datasheet, as these depend on your data rate (ODR). We will label these according to the 95Hz column, but of course the actual cutoff frequency depends on ODR.

| enum G_HPM_T |

CRTL_REG2_G_HPM values

| enum CTRL_REG3_G_BITS_T |

Gyro CTRL_REG3_G bits (interrupt G config)

| enum CTRL_REG4_G_BITS_T |

Gyro CTRL_REG4_G bits

| enum G_ST_T |

CRTL_REG4_G_ST values

| enum G_FS_T |

CRTL_REG4_G_FS values

| enum CTRL_REG5_G_BITS_T |

Gyro CTRL_REG5_G bits

| enum G_INT1OUTSEL_T |

CRTL_REG5_G_OUTSEL and INT1SEL values. See Figure 18 in the datasheet.

| enum STATUS_REG_G_BITS_T |

Gyro STATUS_REG_G bits

| enum FIFO_CTRL_REG_G_T |

Gyro FIFO_CTRL_REG_G bits

| enum G_FM_T |

FIFO_CTRL_REG_G_FM values (FIFO Modes)

| enum FIFO_SRC_REG_G_BITS_T |

FIFO_SRC_REG_G bits

| enum INT1_CFG_G_BITS_T |

INT1_CFG_G bits

| enum INT1_SRC_G_BITS_T |

INT1_SRC_G bits

| enum REG_XM_T |

LSM9DS0 Accelerometer (X) and Magnetometer (M) registers

| enum STATUS_REG_M_BITS_T |

XM STATUS_REG_M bits

| enum INT_CTRL_REG_M_BITS_T |

INT_CTRL_REG_M bits

| enum INT_SRC_REG_M_BITS_T |

INT_SRC_REG_M bits

| enum CTRL_REG0_XM_BITS_T |

CTRL_REG0_XM bits

| enum CTRL_REG1_XM_BITS_T |

CTRL_REG1_XM bits

| enum XM_AODR_T |

CTRL_REG1_XM_AODR values

| enum CTRL_REG2_XM_BITS_T |

CTRL_REG2_XM bits

| enum XM_AST_T |

CTRL_REG2_XM_AST values

| enum XM_AFS_T |

CTRL_REG2_XM_AFS (accel full scale) values

| enum XM_ABW_T |

CTRL_REG2_XM_ABW (accel anti-alias filter bandwidth) values

| enum CTRL_REG3_XM_BITS_T |

CTRL_REG3_XM bits

| enum CTRL_REG4_XM_BITS_T |

CTRL_REG4_XM bits

| enum CTRL_REG5_XM_BITS_T |

CTRL_REG5_XM bits

| enum XM_ODR_T |

CTRL_REG5_XM_ODR (magnetometer output data rate) values

| enum XM_RES_T |

CTRL_REG5_XM_RES (magnetometer resolution) values

| enum CTRL_REG6_XM_BITS_T |

CTRL_REG6_XM bits

| enum XM_MFS_T |

CTRL_REG6_XM_MFS (magnetometer full scale) values

| enum CTRL_REG7_XM_BITS_T |

CTRL_REG7_XM bits

| enum XM_MD_T |

CTRL_REG7_XM_MD (magnetometer sensor mode) values

| enum XM_AHPM_T |

CTRL_REG7_AHPM_MD (accel high-pass filter mode) values

| enum STATUS_REG_A_BITS_T |

XM STATUS_REG_A bits

| enum FIFO_CTRL_REG_T |

XM FIFO_CTRL_REG bits

| enum FM_T |

XM FIFO_CTRL_REG_FM values (FIFO Modes)

| enum FIFO_SRC_REG_BITS_T |

FIFO_SRC_REG bits

| enum INT_GEN_X_REG_BITS_T |

INT_GEN_1_REG and INT_GEN_2_REG (GEN_X) bits

| enum INT_GEN_X_SRC_BITS_T |

INT_GEN_1_SRC and INT_GEN_2_SRC (GEN_X) bits

| enum INT_GEN_X_THS_BITS_T |

INT_GEN_1_THS and INT_GEN_2_THS (GEN_X) bits

| enum INT_GEN_X_DUR_BITS_T |

INT_GEN_1_DUR and INT_GEN_2_DUR (GEN_X) bits

| enum CLICK_CONFIG_BITS_T |

CLICK_CONFIG bits

| enum CLICK_SRC_BITS_T |

CLICK_SRC bits

| enum CLICK_THS_BITS_T |

CLICK_THS bits

| enum CLICK_TIME_LIMIT_BITS_T |

CLICK_TIME_LIMIT bits

| enum ACT_THS_BITS_T |

ACT_THS (sleep-to-wake/return-to-sleep activation threshold) bits

|

1.8.9.1

1.8.9.1